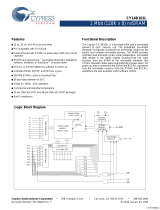

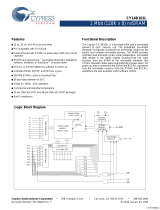

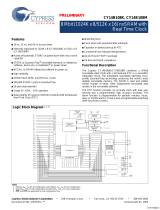

Cypress CY14B101NA is a 1-Mbit nonvolatile static RAM (nvSRAM) with a fast access time of 20 ns. It is organized as 128K bytes of 8 bits each or 64K words of 16 bits each. The 48-ball FBGA, 44-pin TSOP - II, 48-pin SSOP, and 32-pin SOIC packages are available.

The CY14B101NA has a number of features that make it ideal for use in a variety of applications, including:

- Fast access time of 20 ns

- Low power consumption

- Single 3V power supply

- Automatic STORE on power down

- Infinite read, write, and recall cycles

The CY14B101NA is a versatile device that can be used in a wide range of applications, including:

Cypress CY14B101NA is a 1-Mbit nonvolatile static RAM (nvSRAM) with a fast access time of 20 ns. It is organized as 128K bytes of 8 bits each or 64K words of 16 bits each. The 48-ball FBGA, 44-pin TSOP - II, 48-pin SSOP, and 32-pin SOIC packages are available.

The CY14B101NA has a number of features that make it ideal for use in a variety of applications, including:

- Fast access time of 20 ns

- Low power consumption

- Single 3V power supply

- Automatic STORE on power down

- Infinite read, write, and recall cycles

The CY14B101NA is a versatile device that can be used in a wide range of applications, including:

-

1

1

-

2

2

-

3

3

-

4

4

-

5

5

-

6

6

-

7

7

-

8

8

-

9

9

-

10

10

-

11

11

-

12

12

-

13

13

-

14

14

-

15

15

-

16

16

-

17

17

-

18

18

-

19

19

-

20

20

-

21

21

-

22

22

-

23

23

-

24

24

-

25

25

Cypress CY14B101NA User manual

- Type

- User manual

- This manual is also suitable for

Cypress CY14B101NA is a 1-Mbit nonvolatile static RAM (nvSRAM) with a fast access time of 20 ns. It is organized as 128K bytes of 8 bits each or 64K words of 16 bits each. The 48-ball FBGA, 44-pin TSOP - II, 48-pin SSOP, and 32-pin SOIC packages are available.

The CY14B101NA has a number of features that make it ideal for use in a variety of applications, including:

- Fast access time of 20 ns

- Low power consumption

- Single 3V power supply

- Automatic STORE on power down

- Infinite read, write, and recall cycles

The CY14B101NA is a versatile device that can be used in a wide range of applications, including:

Ask a question and I''ll find the answer in the document

Finding information in a document is now easier with AI

Related papers

-

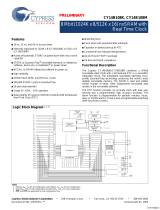

Cypress CY14E102N User manual

Cypress CY14E102N User manual

-

Cypress Perform CY14B102N User manual

Cypress Perform CY14B102N User manual

-

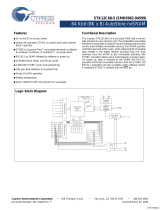

Cypress CY14B108L User manual

Cypress CY14B108L User manual

-

Cypress CY14B104NA User manual

Cypress CY14B104NA User manual

-

Cypress CY14B104M User manual

Cypress CY14B104M User manual

-

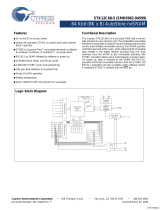

Cypress STK22C48 User manual

Cypress STK22C48 User manual

-

Cypress CY14B101L User manual

Cypress CY14B101L User manual

-

Cypress CY14B108M User manual

Cypress CY14B108M User manual

-

Cypress CY14E256L User manual

Cypress CY14E256L User manual

-

Cypress SMD5962-94599 User manual

Cypress SMD5962-94599 User manual

Other documents

-

Cypress Semiconductor Perform STK14D88 User manual

-

Cypress Semiconductor S29JL064J User manual

-

Sharp 00ZFO3MKCUSME User manual

-

Sharp FO-1MK User manual

-

Icop ICOP-4087 Owner's manual

-

NXP DSP56009EVM User guide

-

Microsemi SmartFusion A2F500-DEV-KIT-2 User manual

-

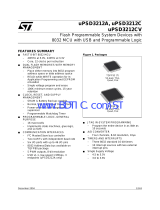

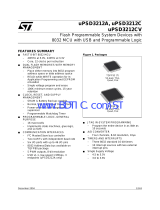

ST & T UPSD3212C User manual

ST & T UPSD3212C User manual

-

Cypress Semiconductor CYALKIT-E03 Quick start guide

-

Delta Tau PMAC MINI PCI Reference guide