OPERATING INSTRUCTIONS

M68302FADS User’s Manual 19

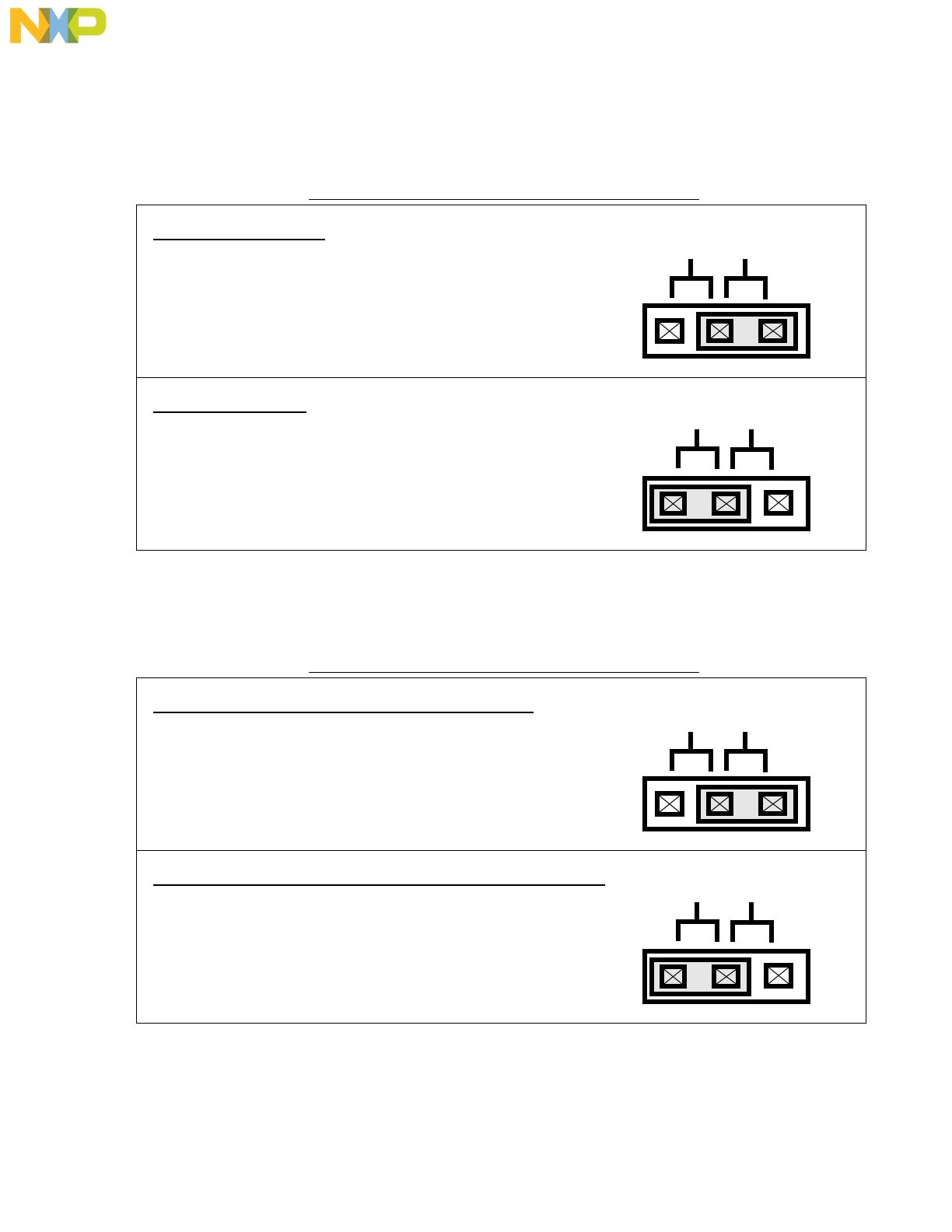

3•2•4 Pchip PLL enable jumper - J2.

The PLL of the Pchip, is controlled by applying or preventing PLL block power, on the VCCSYN pin. The

selection, is done with J2 jumper, as shown in FIGURE 1-10.

FIGURE 1-11 Pchip PLL enable jumper (J2)

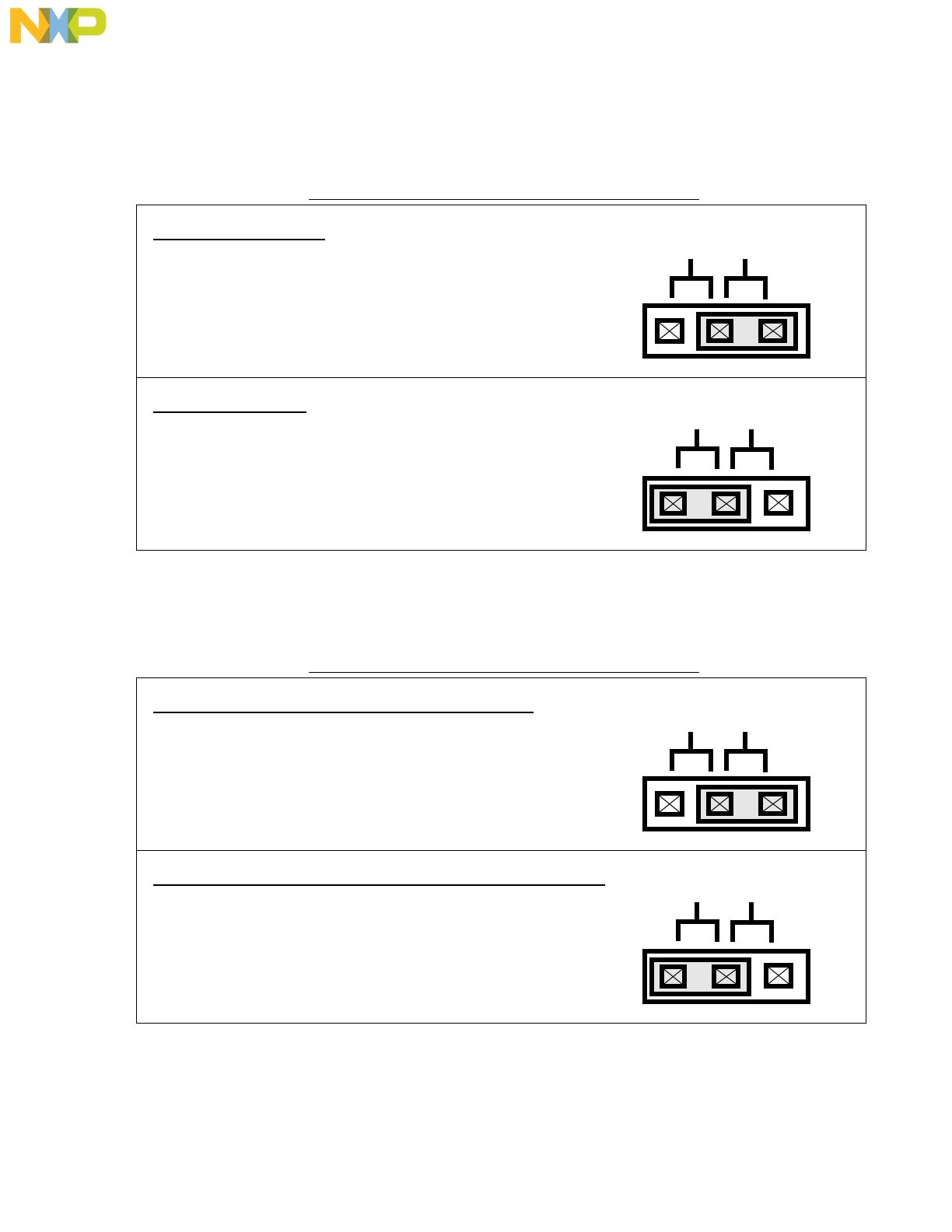

3•2•5 PCMCIA power source selection - J3.

The PCMCIA block in the Pchip, can be powered by one of two sources. The first is the board common

VCC supply and the second is an external power, supplied through a PC host, plugged into the PCMCIA

connector. The selection, is done with J3 jumper, as shown in FIGURE 1-12.

FIGURE 1-12 Pchip PLL enable jumper (J3)

1

Pchip PLL - Disabled

Pchip PLL enabled

Pchip PLL

ON OFF

Pchip PLL

ON OFF

When the jumper is installed on pins 2 - 3, the

Pchip PLL is disabled. This actually shorts the

Pchip VCCSYN pin, to ground.

When the jumper is installed between pins 1 - 2,

the Pchip PLL is enabled. This actually connects

VCCSYN pin of the Pchip to VCC.

1

Pchip PCMCIA block is powered by a host PC

Pchip PCMCIA block is powered by board supply board

PCMCIA PWR

INT PC

When the jumper is installed on pins 2 - 3, the

Pchip PCMCIA block, get its power from a host

PC, connected to PCMCIA connector - P4.

When the jumper is installed on pins 1 - 2, the

Pchip PCMCIA block, get its power from the

board common supply.

PCMCIA PWR

INT PC

Frees

cale Semiconductor,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...