Elixir M2F2G64CB88DHN-CG Datasheet

- Category

- Memory modules

- Type

- Datasheet

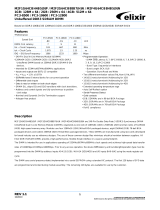

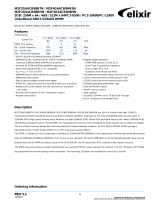

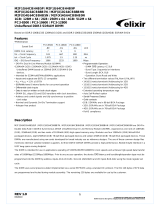

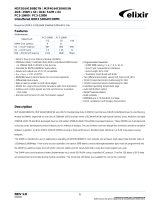

Elixir M2F2G64CB88DHN-CG is a 2GB DDR3 SDRAM DIMM designed for use in applications operating at 533MHz/667MHz clock speeds. It achieves high-speed data transfer rates of 1066Mbps/1333Mbps and provides a high-performance, flexible 8-byte interface in a 5.25” long space-saving footprint. With its programmable operation, it offers various CAS latencies, burst types, burst lengths, and operation modes for customized performance.

Elixir M2F2G64CB88DHN-CG is a 2GB DDR3 SDRAM DIMM designed for use in applications operating at 533MHz/667MHz clock speeds. It achieves high-speed data transfer rates of 1066Mbps/1333Mbps and provides a high-performance, flexible 8-byte interface in a 5.25” long space-saving footprint. With its programmable operation, it offers various CAS latencies, burst types, burst lengths, and operation modes for customized performance.

-

1

1

-

2

2

-

3

3

-

4

4

-

5

5

-

6

6

-

7

7

-

8

8

-

9

9

-

10

10

-

11

11

-

12

12

-

13

13

-

14

14

-

15

15

-

16

16

-

17

17

-

18

18

-

19

19

-

20

20

-

21

21

-

22

22

Elixir M2F2G64CB88DHN-CG Datasheet

- Category

- Memory modules

- Type

- Datasheet

Elixir M2F2G64CB88DHN-CG is a 2GB DDR3 SDRAM DIMM designed for use in applications operating at 533MHz/667MHz clock speeds. It achieves high-speed data transfer rates of 1066Mbps/1333Mbps and provides a high-performance, flexible 8-byte interface in a 5.25” long space-saving footprint. With its programmable operation, it offers various CAS latencies, burst types, burst lengths, and operation modes for customized performance.

Ask a question and I''ll find the answer in the document

Finding information in a document is now easier with AI

Related papers

-

Elixir M2F4G64CB8HB5N-CG Datasheet

Elixir M2F4G64CB8HB5N-CG Datasheet

-

Elixir M2F2G64CB88B7N-CG Datasheet

Elixir M2F2G64CB88B7N-CG Datasheet

-

Elixir M2F1G64CBH4B5P-CG Datasheet

Elixir M2F1G64CBH4B5P-CG Datasheet

-

Elixir M2S4G64CB8HG5N-CG Datasheet

Elixir M2S4G64CB8HG5N-CG Datasheet

-

Elixir M2F4G64CB8HG5N-CG Datasheet

Elixir M2F4G64CB8HG5N-CG Datasheet

-

Elixir M2Y2G64CB8HC5N-CG Datasheet

-

Elixir M2N2G64CB8HA5N-CG Datasheet

Elixir M2N2G64CB8HA5N-CG Datasheet

-

Elixir M2X4G64CB8HG5N-DG User manual

Elixir M2X4G64CB8HG5N-DG User manual

-

Elixir M2Y2G64CB8HA9NDG User manual

Elixir M2Y2G64CB8HA9NDG User manual

-

Elixir M2F2G64CB8HA4N-CG Datasheet

Elixir M2F2G64CB8HA4N-CG Datasheet

Other documents

-

Hynix HMT41GU7MFR8C-H9 Datasheet

Hynix HMT41GU7MFR8C-H9 Datasheet

-

Transcend TS1GSK64V6H Datasheet

-

Hynix HMT351U6CFR8C-H9N0 User manual

Hynix HMT351U6CFR8C-H9N0 User manual

-

Hynix HMT351U7CFR8A-PBT0 Datasheet

Hynix HMT351U7CFR8A-PBT0 Datasheet

-

Transcend TS1GLK72V6H Datasheet

-

Hynix HMT451U7AFR8C-PBT0 Datasheet

Hynix HMT451U7AFR8C-PBT0 Datasheet

-

Transcend TS2GKR72V8Z Datasheet

-

Samsung M471B1G73AH0 User manual

-

Super Talent Technology W1333UA2GV Datasheet

-

Silicon Power SP002GBLTU133S02 Datasheet