Hitachi Single-Chip Microcomputer

H8/3150 Series

H8/3152

HD6483152

H8/3153

HD6483153

H8/3155

HD6483155

H8/3156

HD6483156

H8/3158

HD6483158

Hardware Manual

ADE-602-182

Rev. 1.0

3/11/99

Hitachi, Ltd.

Cautions

1. Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s

patent, copyright, trademark, or other intellectual property rights for information contained in

this document. Hitachi bears no responsibility for problems that may arise with third party’s

rights, including intellectual property rights, in connection with use of the information

contained in this document.

2. Products and product specifications may be subject to change without notice. Confirm that you

have received the latest product standards or specifications before final design, purchase or

use.

3. Hitachi makes every attempt to ensure that its products are of high quality and reliability.

However, contact Hitachi’s sales office before using the product in an application that

demands especially high quality and reliability or where its failure or malfunction may directly

threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear

power, combustion control, transportation, traffic, safety equipment or medical equipment for

life support.

4. Design your application so that the product is used within the ranges guaranteed by Hitachi

particularly for maximum rating, operating supply voltage range, heat radiation characteristics,

installation conditions and other characteristics. Hitachi bears no responsibility for failure or

damage when used beyond the guaranteed ranges. Even within the guaranteed ranges,

consider normally foreseeable failure rates or failure modes in semiconductor devices and

employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi

product does not cause bodily injury, fire or other consequential damage due to operation of

the Hitachi product.

5. This product is not designed to be radiation resistant.

6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document

without written approval from Hitachi.

7. Contact Hitachi’s sales office for any questions regarding this document or Hitachi

semiconductor products.

Preface

The H8/3150 series is a single-chip microcomputer built around a high-speed H8/300 CPU core.

On-chip facilities include an EEPROM, a ROM, a RAM, two I/O ports, a random number

generator (RNG), and a watchdog timer (WDT).

On-chip EEPROM makes the H8/3150 series ideal for applications requiring nonvolatile data

storage, including smart cards and portable data banks. Security functions protect data in the

internal memory against illegal external reading and writing.

This manual describes the H8/3150 series hardware. For details of the instruction set, refer to the

H8/300 Series Programming Manual.

i

Contents

Section 1 Overview.......................................................................................... 1

1.1 Overview............................................................................................................................ 1

1.2 Block Diagram................................................................................................................... 4

1.3 Pin Arrangement and Functions........................................................................................ 5

1.3.1 Pin Arrangement .................................................................................................. 5

1.3.2 Pin Functions........................................................................................................ 7

Section 2 CPU.................................................................................................. 9

2.1 Overview............................................................................................................................ 9

2.1.1 Features ................................................................................................................ 9

2.1.2 CPU Registers ...................................................................................................... 11

2.2 Register Descriptions......................................................................................................... 12

2.2.1 General Registers.................................................................................................. 12

2.2.2 Control Registers.................................................................................................. 12

2.2.3 Initial Register Values.......................................................................................... 14

2.3 Data Formats...................................................................................................................... 14

2.3.1 Data Formats in General Registers....................................................................... 15

2.3.2 Memory Data Formats.......................................................................................... 16

2.4 Addressing Modes.............................................................................................................17

2.4.1 Addressing Modes................................................................................................ 17

2.4.2 Effective Address Calculation.............................................................................. 19

2.5 Instruction Set.................................................................................................................... 22

2.5.1 Data Transfer Instructions.................................................................................... 24

2.5.2 Arithmetic Operations.......................................................................................... 26

2.5.3 Logic Operations.................................................................................................. 27

2.5.4 Shift Operations.................................................................................................... 27

2.5.5 Bit Manipulations................................................................................................. 29

2.5.6 Branching Instructions.......................................................................................... 33

2.5.7 System Control Instructions................................................................................. 35

2.5.8 EEPROM Write Instruction ................................................................................. 36

2.6 Operating States................................................................................................................. 37

2.6.1 Overview.............................................................................................................. 37

2.6.2 Program Execution State...................................................................................... 38

2.6.3 Exception-Handling State .................................................................................... 38

2.6.4 Power-Down State................................................................................................ 38

2.7 Exception Handling...........................................................................................................39

2.7.1 Overview.............................................................................................................. 39

2.7.2 Reset..................................................................................................................... 40

2.7.3 Interrupts .............................................................................................................. 40

ii

2.7.4 Reset Start Timing................................................................................................ 41

2.8 Power-Down State.............................................................................................................42

2.8.1 Overview.............................................................................................................. 42

2.8.2 Transition to Sleep Mode ..................................................................................... 42

2.8.3 Exit from Sleep Mode .......................................................................................... 43

Section 3 Memory Maps.................................................................................. 45

Section 4 Random Number Generator (RNG)................................................. 51

4.1 Overview............................................................................................................................ 51

4.1.1 Features ................................................................................................................ 51

4.1.2 Register Configuration ......................................................................................... 51

4.2 Register Descriptions......................................................................................................... 52

4.2.1 RNG Control Status Register (RCSR) ................................................................. 52

4.2.2 RNG Result Register (RNRR).............................................................................. 53

4.3 Operation ........................................................................................................................... 54

4.4 Notes on Usage.................................................................................................................. 55

Section 5 Watchdog Timer (WDT)................................................................. 57

5.1 Overview............................................................................................................................ 57

5.1.1 Features ................................................................................................................ 57

5.1.2 Block Diagram...................................................................................................... 58

5.1.3 Register Configuration ......................................................................................... 58

5.1.4 Vector Configuration............................................................................................ 59

5.2 Register Descriptions......................................................................................................... 59

5.2.1 Timer Counter (TCNT)........................................................................................ 59

5.2.2 Timer Control/Status Register (TCSR)................................................................ 60

5.2.3 Timer Counter Write Address (TCWA)............................................................... 61

5.3 Operation ........................................................................................................................... 63

5.3.1 Checking Application Program Execution Area.................................................. 63

5.3.2 Checking the Procedure for Writing to EEPROM............................................... 65

5.3.3 Reloading TCNT by TCWA Function................................................................. 67

5.3.4 Initializing WDT .................................................................................................. 69

5.4 Notes on Usage.................................................................................................................. 70

Section 6 RAM................................................................................................ 71

6.1 Overview............................................................................................................................ 71

6.1.1 Block Diagram...................................................................................................... 71

Section 7 ROM................................................................................................ 73

7.1 Overview............................................................................................................................ 73

7.1.1 Block Diagram...................................................................................................... 73

iii

Section 8 EEPROM ......................................................................................... 77

8.1 Overview............................................................................................................................ 77

8.1.1 Features ................................................................................................................ 77

8.1.2 Block Diagram...................................................................................................... 78

8.1.3 Memory Organization .......................................................................................... 79

8.1.4 Register Configuration ......................................................................................... 81

8.2 Register Descriptions......................................................................................................... 82

8.2.1 EEPROM Control Register (ECR)....................................................................... 82

8.2.2 EEPROM Protection Register (EPR)................................................................... 83

8.3 EEPROM Read Operation ................................................................................................ 83

8.4 EEPROM Write and Erase Operations.............................................................................. 84

8.4.1 Write/Erase Sequence .......................................................................................... 84

8.4.2 Rewrite ................................................................................................................. 86

8.4.3 Erase..................................................................................................................... 87

8.4.4 Overwrite.............................................................................................................. 87

8.5 Write/Erase Protection.......................................................................................................88

8.5.1 Protect Bits ........................................................................................................... 88

8.5.2 Protection Procedure ............................................................................................ 89

8.5.3 Reading the Protect Bits....................................................................................... 91

8.6 Notes on Usage.................................................................................................................. 92

8.7 Notes on Usage of H8/3153 .............................................................................................. 94

Section 9 I/O Ports........................................................................................... 97

9.1 Overview............................................................................................................................ 97

9.1.1 Block Diagram...................................................................................................... 97

9.1.2 Register Configuration ......................................................................................... 99

9.2 Register Descriptions......................................................................................................... 99

9.2.1 Data Register (DR)............................................................................................... 99

9.2.2 Data Direction Register (DDR)............................................................................ 100

9.3 Pin Functions..................................................................................................................... 100

Section 10 Clock Pulse Generator .....................................................................103

10.1 Overview............................................................................................................................ 103

10.2 System Control Register.................................................................................................... 104

Section 11 Security............................................................................................105

11.1 Overview............................................................................................................................ 105

11.2 Error Detection in Sleep Mode.......................................................................................... 105

Section 12 Electrical Characteristics..................................................................107

12.1 Absolute Maximum Ratings.............................................................................................. 107

12.2 Electrical Characteristics................................................................................................... 108

12.2.1 DC Characteristics (5 V, CPU operates at half of the external clock frequency) 109

iv

12.2.2 AC Characteristics (5 V, CPU operates at half of the external clock frequency) 110

12.2.3 DC Characteristics (5 V, CPU operates at the external clock frequency)............ 111

12.2.4 AC Characteristics (5 V, CPU operates at the external clock frequency)............ 112

12.2.5 DC Characteristics (3 V, CPU operates at half of the external clock frequency) 114

12.2.6 AC Characteristics (3 V, CPU operates at half of the external clock frequency) 115

12.2.7 DC Characteristics (3 V, CPU operates at the external clock frequency)............ 116

12.2.8 AC Characteristics (3 V, CPU operates at the external clock frequency)............ 117

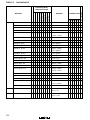

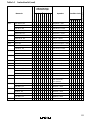

Appendix A Instruction Set...............................................................................119

Appendix B Operation Code Map.....................................................................127

Appendix C Register Field................................................................................129

C.1 Register Field (1)............................................................................................................... 129

C.2 Register Field (2)............................................................................................................... 130

Appendix D Comparison with H8/3102, H8/3103............................................135

Appendix E H8/3150 Series DP-64S Pin Arrangement....................................138

1

Section 1 Overview

1.1 Overview

The H8/3150 series is a single-chip microcomputer unit (MCU) built around a high-speed H8/300

CPU core. An EEPROM, a ROM, a RAM, two I/O ports, a random number generator (RNG), and

a watchdog timer (WDT) are integrated onto the H8/3150 series chip.

Operating at a maximum 5-MHz internal clock rate at 5 V, the H8/300 CPU rapidly executes bit-

manipulation instructions, arithmetic and logic instructions, and data transfer instructions.

Table 1.1 lists the features of the H8/3150 series.

Table 1.1 Features

Item Specification

CPU H8/300 CPU

Two-way general register configuration

• Sixteen 8-bit registers, or

• Eight 16-bit registers

High-speed operation

• Maximum clock rate: internal clock 5 MHz (at 5 V)

• Add/subtract: 0.4 µs

• Multiply/divide: 2.8 µs

Streamlined, concise instruction set

• Instruction length: 2 or 4 bytes

• Register-register arithmetic and logic operations

• MOV instruction for data transfer between registers and memory

Instruction set features

• Multiply instruction (8 bits × 8 bits)

• Divide instruction (16 bits ÷ 8 bits)

• Bit-accumulator instructions

Register-indirect specification of bit positions

• EEPROM write instruction (EEPMOV instruction)

2

Table 1.1 Features (cont)

Item Specification

On-chip memory EEPROM

H8/3152: 8 kbytes + 256 bytes (32 bytes x (256 + 8) pages)

H8/3153: 16 kbytes + 512 bytes (64 bytes x (256 + 8) pages)

H8/3155: 1 kbyte + 128 bytes (16 bytes x (64 + 8) pages)

H8/3156: 2 kbyte + 128 bytes (16 bytes x (128 + 8) pages)

H8/3158: 16 kbytes + 512 bytes (64 bytes x (256 + 8) pages)

• Written by a special block data transfer instruction

• Page write (1 byte to page capacity) and erase

• Protected against accidental writing and erasing

• On-chip voltage pumping circuit

• Built-in oscillator and timer

• Write/erase time (max.): 10 ms (rewrite), 5 ms (erase, overwrite)

• Rewrite endurance: 10

5

times

• Data retention time: 10 years

ROM

H8/3152: 24 kbytes

H8/3153: 32 kbytes

H8/3155: 16 kbytes

H8/3156: 16 kbytes

H8/3158: 46 kbytes

RAM

H8/3152: 512 bytes

H8/3153: 1 kbyte

H8/3155: 512 bytes

H8/3156: 512 bytes

H8/3158: 1 kbyte

I/O ports Two general-purpose input/output ports (Also used for interrupts)

Note: When writing to the DDR7 and DDR6 bits, use the MOV instruction

instead of the bit manipulation instruction.

Random number

generator (RNG)

Generates 16-bit random numbers.

3

Table 1.1 Features (cont)

Item Specification

Watchdog timer

(WDT)

(option)

• Issues a UDF interrupt at a required interval.

• Issues an EWE interrupt before an EEPMOV instruction is executed.

• Stops the on-chip functions when the halt flag is set.

• One of four counter clock sources can be selected.

Note: Specify whether to operate or stop the WDT for each ROM code. If

specifying that the WDT stops, do not access WDT control registers.

Interrupts Two external interrupt pins: I/O-1/IRQ and I/O-2/IRQ

• Used for interrupt input in sleep mode

• Same exception handling vector is assigned to both interrupts

Two internal interrupts: EWE and UDF from WDT

Note: When sleep mode is entered, set DDR to 0 to use the pins as I/O input

ports before executing a SLEEP instruction. When writing to the DDR7 and

DDR6 bits, use the MOV instruction instead of the bit manipulation

instruction.

Power Single-voltage power supply

• 4.5 V to 5.5 V

• 2.7 V to 3.3 V

Clock frequency

range

When the CPU operates at the external clock frequency (CPUCS0 = 1):

• f

CLK

= 1 MHz to 5 MHz (V

CC

= 4.5 V to 5.5 V)

• f

CLK

= 1 MHz to 4 MHz (V

CC

= 2.7 V to 3.3 V)

When the CPU operates at half of the external clock frequency

(CPUCS0 = 0):

• f

CLK

= 1 MHz to 10 MHz (V

CC

= 4.5 V to 5.5 V) *

• f

CLK

= 1 MHz to 5 MHz (V

CC

= 2.7 V to 3.3 V) *

(f

CLK

: External clock frequency)

Note*: For H8/3153, f

CLK

= 1 MHz to 5 MHz (V

CC

= 4.5 V to 5.5 V), and

f

CLK

= 1 MHz to 4 MHz (V

CC

= 2.7 V to 3.3 V).

Operating

temperature

–25 to +85°C

Power-down state Sleep mode (The sleep mode is entered by the SLEEP instruction)

Security • High frequency detector

• High voltage detector

• Low frequency detector

• Low voltage detector

• Illegal access detector

4

1.2 Block Diagram

Figure 1.1 shows an internal block diagram of the H8/3150 series.

H8/300 CPU

System control logic

ROM

RAM

EEPROM

RNG

I/O port

WDT

I/O-1/IRQ

I/O-2/IRQ

Data bus

Address bus

Clock

divider

V

CC

V

SS

CLK

RES

Security logic

Figure 1.1 Block Diagram

5

1.3 Pin Arrangement and Functions

1.3.1 Pin Arrangement

Figure 1.2 shows the standard COT (chip on tape) pattern of the H8/3150 series. Figure 1.3 shows

the bonding pad arrangement of the wafer product. The COT is mounted on a tape.

V

CC

RES

CLK

NC

V

SS

NC

I/O-1/IRQ

NC

Figure 1.2 Standard COT Pattern (Electrode Surface)

6

I/O-1/IRQ

V

SS

I/O-2/IRQ

CLK

V

CC

RES

User PAD

Note:

This figure shows the relative locations of the bonding pads

on the chip. For accurate locations and chip dimensions,

refer to the separately supplied specifications.

Figure 1.3 Bonding Pad Arrangement

7

1.3.2 Pin Functions

Table 1.2 lists the functions of the H8/3150 series pins.

Table 1.2 Pin Functions

Type Symbol I/O Name and Description

Power supply V

CC

I Power supply: 4.5 V to 5.5 V or 2.7 V to 3.3 V

V

SS

I Ground: 0 V

Clock CLK I Clock: External clock input

Reset RES*

1

I Reset: Low input resets the chip.

Ports I/O-1/IRQ*

2

I/O I/O port 1: One-bit data input/output port. Software can

select input or output.

Interrupt: In sleep mode, this port can receive interrupt

input.

I/O-2/IRQ*

2

I/O I/O port 2: One-bit data input/output port. Software can

select input or output.

Interrupt: In sleep mode, this port can receive interrupt

input.

Notes: 1. An input pull-up MOS is connected to the RES pin as shown in figure 1.4.

Input pull-up MOS

Input buffer

Internal

RES signal

V

CC

RES

pin

Figure 1.4 Block Diagram of RES Pin

2. The I/O-1/IRQ and I/O-2/IRQ pins can be used as I/O ports and interrupt input pins.

When these pins are not used, they must be left open.

Input pull-up MOS's are connected to these pins.

See section 9, I/O Ports, for I/O-1/IRQ and I/O-2/IRQ specification details.

9

Section 2 CPU

2.1 Overview

The H8/3150 series has an H8/300 CPU: an 8-bit central processing unit with a speed-oriented

architecture featuring sixteen 8-bit general registers (or eight 16-bit general registers). This section

describes the CPU features and functions, including a concise description of the addressing modes

and instruction set. For further details on the instructions, see the H8/300 Series Programming

Manual.

2.1.1 Features

The main features of the H8/300 CPU are listed below.

• Two-way register configuration

Sixteen 8-bit general registers, or

Eight 16-bit general registers

• Instruction set with 55 basic instructions*, including:

Multiply and divide instructions

Powerful bit-manipulation instructions

EEPROM write instruction

• Eight addressing modes

Register direct: Rn

Register indirect: @Rn

Register indirect with displacement: @(d:16, Rn)

Register indirect with post-increment or pre-decrement: @Rn+ or @–Rn

Absolute address: @aa:8 or @aa:16

Immediate: #xx:8 or #xx:16

Program-counter relative: @(d:8, PC)

Memory indirect: @@aa:8

• 64-kbyte address space

Note: * The H8/300 CPU has 57 basic instructions, but the H8/3150 series uses only 55 of them.

The MOVFPE and MOVTPE instructions are not used.

10

• High-speed operation

Every frequently-used instruction is executed in two to four states

Maximum clock rate is 5-MHz internal clock (at 5 V)

• 8- or 16-bit register-register add or subtract: 0.4 µs

• 8 × 8-bit multiply: 2.8 µs

• 16 ÷ 8-bit divide: 2.8 µs

• Power-down states

Entered by the SLEEP instruction

11

2.1.2 CPU Registers

Figure 2.1 shows the register structure of the H8/300 CPU. There are two groups of registers:

general registers and control registers.

76543210

I UHUNZVCCCR

PC

(SP)

0707

R0H

R1H

R2H

R3H

R4H

R5H

R6H

R7H

R0L

R1L

R2L

R3L

R4L

R5L

R6L

R7L

General registers (Rn)

Control registers (CR)

15 0

Legend:

SP:

PC:

CCR:

I:

U:

H:

N:

Z:

V:

C:

Stack pointer

Program counter

Condition code register

Interrupt mask bit

User bit

Half-carry flag

Negative flag

Zero flag

Overflow flag

Carry flag

Figure 2.1 CPU Registers

12

2.2 Register Descriptions

2.2.1 General Registers

All the general registers can be used as both data registers and address registers.

When used as data registers, they can be accessed as 16-bit registers (R0 to R7), or the high bytes

(R0H to R7H) and low bytes (R0L to R7L) can be accessed separately as 8-bit registers.

When used as address registers, the general registers are accessed as 16-bit registers (R0 to R7).

Registers R4L, R5, and R6 have special functions when the EEPMOV (EEPROM write)

instruction is executed.

R7 also functions as the stack pointer, used implicitly by hardware in exception handling and

subroutine calls. In assembly-language coding, R7 can also be denoted by the symbol SP. As

indicated in figure 2.2, SP (R7) points to the top of the stack.

SP (R7)

Free area

Stack area

Figure 2.2 Stack Pointer

2.2.2 Control Registers

The CPU control registers include a 16-bit program counter (PC) and an 8-bit condition code

register (CCR).

(1) Program Counter (PC): This 16-bit register indicates the address of the next instruction the

CPU will execute. All instructions are fetched 16 bits (1 word) at a time, so the least significant bit

of PC is ignored (always regarded as 0).

13

(2) Condition Code Register (CCR): This 8-bit register contains internal CPU status

information, including the interrupt mask bit (I) and half-carry (H), negative (N), zero (Z),

overflow (V), and carry (C) flags.

Bit 7—Interrupt Mask Bit (I): Masks interrupts when set to 1. This bit is set to 1 at the

beginning of exception handling.

Bit 6—User Bit (U): Can be written and read by software for its own purposes (using the LDC,

STC, ANDC, ORC, and XORC instructions).

Bit 5—Half-Carry Flag (H): When the ADD.B, ADDX.B, SUB.B, SUBX.B, CMP.B, or NEG.B

instruction is executed, this flag is set to 1 if there is a carry or borrow at bit 3, and is cleared to 0

otherwise.

The H flag is used implicitly by the DAA and DAS instructions.

When the ADD.W, SUB.W, or CMP.W instruction is executed, the H flag is set to 1 if there is a

carry or borrow at bit 11, and is cleared to 0 otherwise.

Bit 4—User Bit (U): Can be written and read by software for its own purposes (using the LDC,

STC, ANDC, ORC, and XORC instructions).

Bit 3—Negative Flag (N): Indicates the most significant bit (sign bit) of data.

Bit 2—Zero Flag (Z): Set to 1 to indicate zero data, and cleared to 0 to indicate non-zero data.

Bit 1—Overflow Flag (V): Set to 1 when an arithmetic overflow occurs, and cleared to 0 at other

times.

Bit 0—Carry Flag (C): Set to 1 when a carry occurs, and cleared to 0 otherwise. Used by:

• Add instructions, to indicate a carry

• Subtract instructions, to indicate a borrow

• Shift and rotate instructions, to store the value shifted out of the end bit

The carry flag is also used as a bit accumulator by bit manipulation instructions.

Some instructions leave some or all of the flag bits unchanged. The LDC, STC, ANDC, ORC, and

XORC instructions enable the CPU to load and store CCR, and to set or clear selected bits by

logic operations. The N, Z, V, and C flags are used as branching conditions for conditional

branching (Bcc) instructions.

Refer to the H8/300 Series Programming Manual for the action of each instruction on the flag

bits.

14

2.2.3 Initial Register Values

When the CPU is reset, the program counter (PC) is loaded from the vector table and the I bit in

CCR is set to 1. The other CCR bits and the general registers are not initialized. In particular, the

stack pointer (R7) is not initialized. To prevent program crashes, the stack pointer should be

initialized by software, by the first instruction executed after a reset.

2.3 Data Formats

The H8/300 CPU can process 1-bit data, 4-bit (BCD) data, 8-bit (byte) data, and 16-bit (word)

data.

• Bit manipulation instructions operate on 1-bit data specified as bit n (n = 0, 1, 2, ..., 7) in a byte

operand.

• All arithmetic instructions except ADDS and SUBS can operate on byte data.

• The MOV.W, ADD.W, SUB.W, CMP.W, ADDS, SUBS, MULXU (8 bits × 8 bits), and

DIVXU (16 bits ÷ 8 bits) instructions operate on word data.

• The DAA and DAS instructions perform decimal arithmetic adjustments on byte data in

packed BCD form. Each nibble of the byte is treated as a decimal digit.

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

-

1

1

-

2

2

-

3

3

-

4

4

-

5

5

-

6

6

-

7

7

-

8

8

-

9

9

-

10

10

-

11

11

-

12

12

-

13

13

-

14

14

-

15

15

-

16

16

-

17

17

-

18

18

-

19

19

-

20

20

-

21

21

-

22

22

-

23

23

-

24

24

-

25

25

-

26

26

-

27

27

-

28

28

-

29

29

-

30

30

-

31

31

-

32

32

-

33

33

-

34

34

-

35

35

-

36

36

-

37

37

-

38

38

-

39

39

-

40

40

-

41

41

-

42

42

-

43

43

-

44

44

-

45

45

-

46

46

-

47

47

-

48

48

-

49

49

-

50

50

-

51

51

-

52

52

-

53

53

-

54

54

-

55

55

-

56

56

-

57

57

-

58

58

-

59

59

-

60

60

-

61

61

-

62

62

-

63

63

-

64

64

-

65

65

-

66

66

-

67

67

-

68

68

-

69

69

-

70

70

-

71

71

-

72

72

-

73

73

-

74

74

-

75

75

-

76

76

-

77

77

-

78

78

-

79

79

-

80

80

-

81

81

-

82

82

-

83

83

-

84

84

-

85

85

-

86

86

-

87

87

-

88

88

-

89

89

-

90

90

-

91

91

-

92

92

-

93

93

-

94

94

-

95

95

-

96

96

-

97

97

-

98

98

-

99

99

-

100

100

-

101

101

-

102

102

-

103

103

-

104

104

-

105

105

-

106

106

-

107

107

-

108

108

-

109

109

-

110

110

-

111

111

-

112

112

-

113

113

-

114

114

-

115

115

-

116

116

-

117

117

-

118

118

-

119

119

-

120

120

-

121

121

-

122

122

-

123

123

-

124

124

-

125

125

-

126

126

-

127

127

-

128

128

-

129

129

-

130

130

-

131

131

-

132

132

-

133

133

-

134

134

-

135

135

-

136

136

-

137

137

-

138

138

Ask a question and I''ll find the answer in the document

Finding information in a document is now easier with AI

Related papers

-

Hitachi H8/3021 User manual

-

Hitachi H8/3670F-ZTAT HD64F3670 User manual

-

Hitachi H8/3008 User manual

-

Hitachi H8/3663 User manual

-

Hitachi HD6433060B User manual

-

Hitachi H8/3812 User manual

-

Hitachi HD64F3062R User manual

-

Hitachi H8/3694 User manual

-

Hitachi H8/3048 User manual

-

Hitachi H8/3637 User manual