Page is loading ...

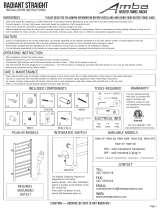

EFM32PG22 Gecko

Reference Manual

The EFM32PG22 family of microcontrollers is part of the Series 2

Gecko portfolio. EFM32PG22 MCUs are ideal for enabling energy-

friendly embedded applications.

The highly efficient solution combines a 76.8 MHz Cortex-M33 with rich analog and com-

munication peripherals to provide an industry-leading, energy efficient MCU for consum-

er and industrial applications.

KEY FEATURES

• 32-bit ARM® Cortex M33 core with up to

76.8 MHz maximum operating frequency

• Up to 512 kB of flash and 32 kB of RAM

• Low energy operation

• 26 uA/MHz

• 1.1 uA sleep (EM2)

• Secure Boot with Root of Trust and

Secure Loader (RTSL)

• 16-bit ADC with 16-channel scan

Timers and Triggers

32-bit bus

Peripheral Reflex System

Serial Interfaces I/O Ports

Analog I/F

Lowest power mode with peripheral operational:

USART

EUART

External

Interrupts

General

Purpose I/O

Pin Reset

Pin Wakeup

ADC

EM4—Shutoff

Energy Management

Brown-Out

Detector

Voltage

Regulator

Power-On

Reset

Security

Clock Management

HF Crystal

Oscillator

LF Crystal

Oscillator

Precision LF

RC Oscillator

HF

RC Oscillator

AES-128, AES-256,

SHA-1, SHA-2,

ECC

Ultra LF RC

Oscillator

Core / Memory

ARM Cortex

TM

M33 processor

with DSP, FPU and TrustZone

ETM Debug Interface RAM Memory

LDMA

Controller

Flash Program

Memory

Real Time

Capture Counter

Timer/Counter

Low Energy Timer Watchdog Timer

Protocol Timer

EM3—StopEM2—Deep SleepEM1—SleepEM0—Active

True Random Number

Generator

Fast Startup

RC Oscillator

Back-Up Real

Time Counter

I

2

C

PDM

DC-DC

Converter

Temperature

Sensor

Secure Boot RTSL

Secure Debug

silabs.com | Building a more connected world. Rev. 1.0

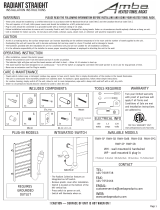

Table of Contents

1. About This Document ...........................23

1.1 Introduction ...............................23

1.2 Conventions ...............................24

1.3 Related Documentation ...........................25

2. System Overview .............................26

2.1 Introduction ...............................26

2.2 Block Diagrams..............................26

2.3 Features overview .............................27

3. System Processor ............................29

3.1 Introduction ...............................29

3.2 Features ................................30

3.3 Functional Description ...........................30

3.3.1 Interrupt Operation ...........................31

3.3.2 TrustZone ..............................31

3.3.3 Interrupt Request Lines (IRQ) .......................32

4. Memory and Bus System ..........................34

4.1 Introduction ...............................34

4.2 Functional Description ...........................35

4.2.1 Bus Matrix ..............................36

4.2.2 Flash ................................37

4.2.3 SRAM ...............................37

4.2.4 Peripherals ..............................37

5. MSC - Memory System Controller ......................43

5.1 Introduction ...............................43

5.2 Features ................................44

5.3 Functional Description ...........................44

5.3.1 Ram Configuration ...........................44

5.3.2 Instruction Cache............................45

5.3.3 Device Information (DI) Page .......................45

5.3.4 User Data (UD) Page Description ......................45

5.3.5 Bootloader ..............................45

5.3.6 Post-reset Behavior ...........................45

5.3.7 Flash Startup .............................45

5.3.8 Flash EM0 / EM1 Power Down .......................46

5.3.9 Wait-states ..............................46

5.3.10 Cortex-M33 If-Then Block Folding......................46

5.3.11 Line Buffering (Prefetch) .........................46

5.3.12 Erase and Write Operations........................47

5.4 DEVINFO - Device Info Page .........................48

5.4.1 DEVINFO Register Map .........................49

silabs.com

| Building a more connected world. Rev. 1.0 | 2

5.4.2 DEVINFO Register Description .......................50

5.5 ICACHE - Instruction Cache .........................76

5.5.1 Cache Operation ............................77

5.5.2 Performance Measurement ........................77

5.5.3 ICACHE Register Map ..........................78

5.5.4 ICACHE Register Description .......................79

5.6 SYSCFG - System Configuration ........................85

5.6.1 Ram Retention ............................85

5.6.2 ECC ................................86

5.6.3 Software Interrupts ...........................86

5.6.4 Bus faults ..............................86

5.6.5 SYSCFG Register Map..........................87

5.6.6 SYSCFG Register Description .......................89

5.7 MSC Register Map ............................97

5.8 MSC Register Description ..........................99

5.8.1 MSC_IPVERSION - IP Version ID ......................99

5.8.2 MSC_READCTRL - Read Control Register ..................100

5.8.3 MSC_WRITECTRL - Write Control Register..................101

5.8.4 MSC_WRITECMD - Write Command Register .................102

5.8.5 MSC_ADDRB - Page Erase/Write Address Buffer ................103

5.8.6 MSC_WDATA - Write Data Register ....................103

5.8.7 MSC_STATUS - Status Register .....................104

5.8.8 MSC_IF - Interrupt Flag Register .....................105

5.8.9 MSC_IEN - Interrupt Enable Register ....................106

5.8.10 MSC_USERDATASIZE - User Data Region Size Register ............107

5.8.11 MSC_CMD - Command Register .....................107

5.8.12 MSC_LOCK - Configuration Lock Register ..................108

5.8.13 MSC_MISCLOCKWORD - Mass Erase and User Data Page Lock Word .......108

5.8.14 MSC_PWRCTRL - Power Control Register .................109

5.8.15 MSC_PAGELOCK0 - Main Space Page 0-31 Lock Word .............110

5.8.16 MSC_PAGELOCK1 - Main Space Page 32-63 Lock Word ............110

6. DBG - Debug Interface ...........................111

6.1 Introduction ..............................111

6.2 Features ...............................111

6.3 Functional Description ..........................112

6.3.1 Debug Pins.............................112

6.3.2 Embedded Trace Macrocell V3.5 (ETM) ...................112

6.3.3 Debug and EM2/EM3 .........................112

6.4 DBG Register Map ...........................113

6.5 DBG Register Description .........................113

6.5.1 DBG_DCIWDATA - Write Data ......................113

6.5.2 DBG_DCIRDATA - Read Data ......................113

6.5.3 DBG_DCISTATUS - Status .......................114

6.5.4 DBG_DCIID - Identification .......................114

6.5.5 DBG_SYSCOM0 - Communication Status ..................115

silabs.com

| Building a more connected world. Rev. 1.0 | 3

6.5.6 DBG_SYSCOM1 - Communication Status ..................116

6.5.7 DBG_SYSPWR0 - Power Status .....................117

6.5.8 DBG_SYSCLK0 - Clocking Status .....................118

6.5.9 DBG_SYSID - Identification .......................120

7. CMU - Clock Management Unit ........................121

7.1 Introduction ..............................121

7.2 Features ...............................121

7.3 Functional Description ..........................122

7.3.1 System Clocks ...........................125

7.3.2 Switching Clock Source ........................128

7.3.3 RC Oscillator Calibration ........................130

7.3.4 Energy Modes ...........................133

7.3.5 Clock Output on a Pin .........................133

7.3.6 Clock Input from a Pin .........................134

7.3.7 Clock Output on PRS .........................134

7.3.8 Interrupts .............................134

7.3.9 Protection .............................134

7.4 CMU Register Map ...........................135

7.5 CMU Register Description .........................138

7.5.1 CMU_IPVERSION - IP Version ID .....................138

7.5.2 CMU_STATUS - Status Register .....................139

7.5.3 CMU_LOCK - Configuration Lock Register ..................140

7.5.4 CMU_WDOGLOCK - WDOG Configuration Lock Register .............140

7.5.5 CMU_IF - Interrupt Flag Register .....................141

7.5.6 CMU_IEN - Interrupt Enable Register ....................141

7.5.7 CMU_CALCMD - Calibration Command Register ................142

7.5.8 CMU_CALCTRL - Calibration Control Register .................143

7.5.9 CMU_CALCNT - Calibration Result Counter Register ..............144

7.5.10 CMU_CLKEN0 - Clock Enable Register 0 ..................145

7.5.11 CMU_CLKEN1 - Clock Enable Register 1 ..................147

7.5.12 CMU_SYSCLKCTRL - System Clock Control .................148

7.5.13 CMU_TRACECLKCTRL - Debug Trace Clock Control ..............149

7.5.14 CMU_EXPORTCLKCTRL - Export Clock Control ...............150

7.5.15 CMU_DPLLREFCLKCTRL - Digital PLL Reference Clock Control ..........152

7.5.16 CMU_EM01GRPACLKCTRL - EM01 Peripheral Group a Clock Control ........152

7.5.17 CMU_EM01GRPBCLKCTRL - EM01 Peripheral Group B Clock Control ........153

7.5.18 CMU_EM23GRPACLKCTRL - EM23 Peripheral Group a Clock Control ........154

7.5.19 CMU_EM4GRPACLKCTRL - EM4 Peripheral Group a Clock Control .........154

7.5.20 CMU_IADCCLKCTRL - IADC Clock Control .................155

7.5.21 CMU_WDOG0CLKCTRL - Watchdog0 Clock Control ..............155

7.5.22 CMU_EUART0CLKCTRL - UART Clock Control ................156

7.5.23 CMU_RTCCCLKCTRL - RTCC Clock Control.................156

7.5.24 CMU_CRYPTOACCCLKCTRL - CRYPTOACC Clock Control ...........157

8. Oscillators ...............................158

8.1 Introduction ..............................158

silabs.com

| Building a more connected world. Rev. 1.0 | 4

8.2 HFXO - High Frequency Crystal Oscillator ....................158

8.2.1 Introduction ............................158

8.2.2 Features .............................158

8.2.3 Functional Description .........................159

8.2.4 HFXO Register Map ..........................162

8.2.5 HFXO Register Description .......................163

8.3 HFRCO - High-Frequency RC Oscillator ....................174

8.3.1 Introduction ............................174

8.3.2 Features .............................174

8.3.3 Functional Description .........................174

8.3.4 HFRCO Register Map .........................177

8.3.5 HFRCO Register Description .......................178

8.4 DPLL - Digital Phased Locked Loop ......................182

8.4.1 Introduction ............................182

8.4.2 Features .............................182

8.4.3 Functional Description .........................182

8.4.4 DPLL Register Map ..........................184

8.4.5 DPLL Register Description .......................185

8.5 LFXO - Low-Frequency Crystal Oscillator ....................190

8.5.1 Introduction ............................190

8.5.2 Features .............................190

8.5.3 Functional Description .........................190

8.5.4 LFXO Register Map ..........................192

8.5.5 LFXO Register Description .......................193

8.6 LFRCO - Low-Frequency RC Oscillator ....................200

8.6.1 Introduction ............................200

8.6.2 Features .............................200

8.6.3 Functional Description .........................200

8.6.4 LFRCO Register Map .........................203

8.6.5 LFRCO Register Description .......................204

8.7 FSRCO - Fast Start RCO .........................211

8.7.1 Introduction ............................211

8.7.2 Features .............................211

8.7.3 Functional Description .........................211

8.7.4 FSRCO Register Map .........................211

8.7.5 FSRCO Register Description .......................212

8.8 ULFRCO - Ultra Low Frequency RC Oscillator ..................212

8.8.1 Introduction ............................212

8.8.2 Features .............................212

8.8.3 Functional Description .........................212

9. SMU - Security Management Unit .......................213

9.1 Introduction ..............................213

9.2 Features ...............................213

9.3 Functional Description ..........................214

9.3.1 Bus Level Security ..........................214

silabs.com

| Building a more connected world. Rev. 1.0 | 5

9.3.2 Privileged Access Control ........................215

9.3.3 Secure Access Control .........................215

9.3.4 ARM TrustZone ...........................216

9.3.5 Configuring Masters ..........................216

9.3.6 Configuring Peripherals ........................216

9.3.7 Configuring Memory ..........................217

9.3.8 Cortex-M33 Integration .........................217

9.3.9 Exception Handling ..........................218

9.3.10 SMU Lock.............................218

9.4 SMU Register Map ...........................219

9.5 SMU Register Description .........................221

9.5.1 SMU_IPVERSION - IP Version ......................221

9.5.2 SMU_STATUS - Status ........................222

9.5.3 SMU_LOCK - Lock ..........................222

9.5.4 SMU_IF - Interrupt Flag ........................223

9.5.5 SMU_IEN - Interrupt Enable .......................224

9.5.6 SMU_M33CTRL - M33 Control ......................225

9.5.7 SMU_PPUPATD0 - PPU PATD Register 0 ..................226

9.5.8 SMU_PPUPATD1 - PPU PATD Register 1 ..................228

9.5.9 SMU_PPUSATD0 - PPU SATD Register 0 ..................230

9.5.10 SMU_PPUSATD1 - PPU SATD Register 1..................232

9.5.11 SMU_PPUFS - PPU Fault Status .....................233

9.5.12 SMU_BMPUPATD0 - BMPU PATD Register 0 ................234

9.5.13 SMU_BMPUSATD0 - BMPU SATD Register 0 ................235

9.5.14 SMU_BMPUFS - BMPU Fault Status ...................235

9.5.15 SMU_BMPUFSADDR - BMPU Fault Status Address ..............236

9.5.16 SMU_ESAURTYPES0 - ESAU Region Types Register 0 .............236

9.5.17 SMU_ESAURTYPES1 - ESAU Region Types Register 1 .............237

9.5.18 SMU_ESAUMRB01 - ESAU Movable Region Boundary 0-1 ............237

9.5.19 SMU_ESAUMRB12 - ESAU Movable Region Boundary 1-2 ............238

9.5.20 SMU_ESAUMRB45 - ESAU Movable Region Boundary 4-5 ............238

9.5.21 SMU_ESAUMRB56 - ESAU Movable Region Boundary 5-6 ............239

10. CRYPTOACC - Cryptographic Accelerator ...................240

10.1 Introduction .............................240

10.2 Features ..............................240

10.3 Cryptographic Functions .........................240

10.3.1 CRYPTOACC_PKCTRL Register Map ...................241

10.3.2 CRYPTOACC_PKCTRL Register Description.................241

10.4 DMA Interface .............................246

10.4.1 CRYPTOACC Register Map ......................246

10.4.2 CRYPTOACC Register Description ....................247

10.5 Random Number Generation ........................260

10.5.1 CRYPTOACC_RNGCTRL Register Map ..................260

10.5.2 CRYPTOACC_RNGCTRL Register Description ................261

11. EMU - Energy Management Unit ......................272

silabs.com

| Building a more connected world. Rev. 1.0 | 6

11.1 Introduction..............................272

11.2 Features ..............................273

11.3 Functional Description ..........................274

11.3.1 Energy Modes ...........................275

11.3.2 Entering Low Energy Modes ......................279

11.3.3 Exiting a Low Energy Mode ......................280

11.3.4 Power Domains ...........................281

11.3.5 Voltage Scaling ...........................281

11.3.6 EM0 / EM1 Peripheral Register Retention ..................282

11.3.7 Power Configurations .........................282

11.3.8 DC-to-DC Interface .........................285

11.3.9 EFP01 Communication ........................288

11.3.10 Brown Out Detector (BOD) ......................289

11.3.11 Reset Management Unit .......................290

11.3.12 Temperature Sensor .........................292

11.3.13 Register Resets ..........................292

11.3.14 Register Locks ...........................293

11.4 EMU Register Map ...........................294

11.5 EMU Register Description .........................296

11.5.1 EMU_DECBOD - DECOUPLE LVBOD Control Register .............296

11.5.2 EMU_BOD3SENSE - BOD3SENSE Control Register ..............297

11.5.3 EMU_VREGVDDCMPCTRL - DC-DC VREGVDD Comparator Control Register .....297

11.5.4 EMU_PD1PARETCTRL - PD1 Partial Retention Control .............298

11.5.5 EMU_LOCK - EMU Configuration Lock Register ................298

11.5.6 EMU_IF - Interrupt Flags ........................299

11.5.7 EMU_IEN - Interrupt Enables ......................300

11.5.8 EMU_EM4CTRL - EM4 Control .....................301

11.5.9 EMU_CMD - EMU Command Register ...................302

11.5.10 EMU_CTRL - EMU Control Register ...................303

11.5.11 EMU_TEMPLIMITS - EMU Temperature Thresholds ..............304

11.5.12 EMU_STATUS - EMU Status Register...................305

11.5.13 EMU_TEMP - Temperature ......................306

11.5.14 EMU_RSTCTRL - Reset Management Control Register .............307

11.5.15 EMU_RSTCAUSE - Reset Cause ....................309

11.5.16 EMU_DGIF - Interrupt Flags Debug ...................310

11.5.17 EMU_DGIEN - Interrupt Enables Debug ..................311

11.5.18 EMU_EFPIF - EFP Interrupt Register ...................311

11.5.19 EMU_EFPIEN - EFP Interrupt Enable Register ................312

11.6 DCDC Register Map ..........................313

11.7 DCDC Register Description ........................314

11.7.1 DCDC_IPVERSION - IPVERSION ....................314

11.7.2 DCDC_EN - Enable .........................314

11.7.3 DCDC_CTRL - Control ........................315

11.7.4 DCDC_EM01CTRL0 - EM01 Control....................316

11.7.5 DCDC_EM23CTRL0 - EM23 Control....................317

11.7.6 DCDC_IF - Interrupt Flags .......................318

11.7.7 DCDC_IEN - Interrupt Enable ......................319

silabs.com

| Building a more connected world. Rev. 1.0 | 7

11.7.8 DCDC_STATUS - Status Register ....................320

11.7.9 DCDC_LOCK - Lock Register ......................321

11.7.10 DCDC_LOCKSTATUS - Lock Status Register ................321

12. PRS - Peripheral Reflex System .......................322

12.1 Introduction..............................322

12.2 Features ..............................322

12.3 Functional Description ..........................323

12.3.1 Asynchronous Channel Functions.....................323

12.3.2 Configurable Logic ..........................324

12.3.3 Producers .............................325

12.3.4 Consumers ............................329

12.4 PRS Register Map ...........................330

12.5 PRS Register Description .........................341

12.5.1 PRS_IPVERSION - IP Version ID .....................341

12.5.2 PRS_ASYNC_SWPULSE - Software Pulse Register ..............342

12.5.3 PRS_ASYNC_SWLEVEL - Software Level Register ..............343

12.5.4 PRS_ASYNC_PEEK - Async Channel Values ................344

12.5.5 PRS_SYNC_PEEK - Sync Channel Values .................345

12.5.6 PRS_ASYNC_CHx_CTRL - Async Channel Control Register ...........346

12.5.7 PRS_SYNC_CHx_CTRL - Sync Channel Control Register ............347

12.5.8 PRS_CONSUMER_CMU_CALDN - CMU CALDN Consumer Selection ........348

12.5.9 PRS_CONSUMER_CMU_CALUP - CMU CALUP Consumer Selection ........348

12.5.10 PRS_CONSUMER_IADC0_SCANTRIGGER - IADC0 SCANTRIGGER Consumer Selection 349

12.5.11 PRS_CONSUMER_IADC0_SINGLETRIGGER - IADC0 SINGLETRIGGER Consumer

Selection .............................349

12.5.12 PRS_CONSUMER_LDMAXBAR_DMAREQ0 - DMAREQ0 Consumer Selection ....350

12.5.13 PRS_CONSUMER_LDMAXBAR_DMAREQ1 - DMAREQ1 Consumer Selection ....350

12.5.14 PRS_CONSUMER_LETIMER0_CLEAR - LETIMER CLEAR Consumer Selection ....351

12.5.15 PRS_CONSUMER_LETIMER0_START - LETIMER START Consumer Selection ....351

12.5.16 PRS_CONSUMER_LETIMER0_STOP - LETIMER STOP Consumer Selection .....352

12.5.17 PRS_CONSUMER_EUART0_RX - EUART0 RX Consumer Register ........352

12.5.18 PRS_CONSUMER_EUART0_TRIGGER - EUART0 TRIGGER Consumer Register ...353

12.5.19 PRS_CONSUMER_RTCC_CC0 - RTCC CC0 Consumer Selection .........353

12.5.20 PRS_CONSUMER_RTCC_CC1 - RTCC CC1 Consumer Selection .........354

12.5.21 PRS_CONSUMER_RTCC_CC2 - RTCC CC2 Consumer Selection .........354

12.5.22 PRS_CONSUMER_CORE_CTIIN0 - CTI0 Consumer Selection ..........355

12.5.23 PRS_CONSUMER_CORE_CTIIN1 - CTI1 Consumer Selection ..........355

12.5.24 PRS_CONSUMER_CORE_CTIIN2 - CTI2 Consumer Selection ..........356

12.5.25 PRS_CONSUMER_CORE_CTIIN3 - CTI3 Consumer Selection ..........356

12.5.26 PRS_CONSUMER_CORE_M33RXEV - M33 Consumer Selection .........357

12.5.27 PRS_CONSUMER_TIMER0_CC0 - TIMER0 CC0 Consumer Selection .......357

12.5.28 PRS_CONSUMER_TIMER0_CC1 - TIMER0 CC1 Consumer Selection .......358

12.5.29 PRS_CONSUMER_TIMER0_CC2 - TIMER0 CC2 Consumer Selection .......358

12.5.30 PRS_CONSUMER_TIMER0_DTI - TIMER0 DTI Consumer Selection ........359

12.5.31 PRS_CONSUMER_TIMER0_DTIFS1 - TIMER0 DTIFS1 Consumer Selection .....359

12.5.32 PRS_CONSUMER_TIMER0_DTIFS2 - TIMER0 DTIFS2 Consumer Selection .....360

silabs.com

| Building a more connected world. Rev. 1.0 | 8

12.5.33 PRS_CONSUMER_TIMER1_CC0 - TIMER1 CC0 Consumer Selection .......360

12.5.34 PRS_CONSUMER_TIMER1_CC1 - TIMER1 CC1 Consumer Selection .......361

12.5.35 PRS_CONSUMER_TIMER1_CC2 - TIMER1 CC2 Consumer Selection .......361

12.5.36 PRS_CONSUMER_TIMER1_DTI - TIMER1 DTI Consumer Selection ........362

12.5.37 PRS_CONSUMER_TIMER1_DTIFS1 - TIMER1 DTIFS1 Consumer Selection .....362

12.5.38 PRS_CONSUMER_TIMER1_DTIFS2 - TIMER1 DTIFS2 Consumer Selection .....363

12.5.39 PRS_CONSUMER_TIMER2_CC0 - TIMER2 CC0 Consumer Selection .......363

12.5.40 PRS_CONSUMER_TIMER2_CC1 - TIMER2 CC1 Consumer Selection .......364

12.5.41 PRS_CONSUMER_TIMER2_CC2 - TIMER2 CC2 Consumer Selection .......364

12.5.42 PRS_CONSUMER_TIMER2_DTI - TIMER2 DTI Consumer Selection ........365

12.5.43 PRS_CONSUMER_TIMER2_DTIFS1 - TIMER2 DTIFS1 Consumer Selection .....365

12.5.44 PRS_CONSUMER_TIMER2_DTIFS2 - TIMER2 DTIFS2 Consumer Selection .....366

12.5.45 PRS_CONSUMER_TIMER3_CC0 - TIMER3 CC0 Consumer Selection .......366

12.5.46 PRS_CONSUMER_TIMER3_CC1 - TIMER3 CC1 Consumer Selection .......367

12.5.47 PRS_CONSUMER_TIMER3_CC2 - TIMER3 CC2 Consumer Selection .......367

12.5.48 PRS_CONSUMER_TIMER3_DTI - TIMER3 DTI Consumer Selection ........368

12.5.49 PRS_CONSUMER_TIMER3_DTIFS1 - TIMER3 DTIFS1 Consumer Selection .....368

12.5.50 PRS_CONSUMER_TIMER3_DTIFS2 - TIMER3 DTIFS2 Consumer Selection .....369

12.5.51 PRS_CONSUMER_TIMER4_CC0 - TIMER4 CC0 Consumer Selection .......369

12.5.52 PRS_CONSUMER_TIMER4_CC1 - TIMER4 CC1 Consumer Selection .......370

12.5.53 PRS_CONSUMER_TIMER4_CC2 - TIMER4 CC2 Consumer Selection .......370

12.5.54 PRS_CONSUMER_TIMER4_DTI - TIMER4 DTI Consumer Selection ........371

12.5.55 PRS_CONSUMER_TIMER4_DTIFS1 - TIMER4 DTIFS1 Consumer Selection .....371

12.5.56 PRS_CONSUMER_TIMER4_DTIFS2 - TIMER4 DTIFS2 Consumer Selection .....372

12.5.57 PRS_CONSUMER_USART0_CLK - USART0 CLK Consumer Selection .......372

12.5.58 PRS_CONSUMER_USART0_IR - USART0 IR Consumer Selection ........373

12.5.59 PRS_CONSUMER_USART0_RX - USART0 RX Consumer Selection ........373

12.5.60 PRS_CONSUMER_USART0_TRIGGER - USART0 TRIGGER Consumer Selection ...374

12.5.61 PRS_CONSUMER_USART1_CLK - USART1 CLK Consumer Selection .......374

12.5.62 PRS_CONSUMER_USART1_IR - USART1 IR Consumer Selection ........375

12.5.63 PRS_CONSUMER_USART1_RX - USART1 RX Consumer Selection ........375

12.5.64 PRS_CONSUMER_USART1_TRIGGER - USART1 TRIGGER Consumer Selection ...376

12.5.65 PRS_CONSUMER_WDOG0_SRC0 - WDOG0 SRC0 Consumer Selection ......376

12.5.66 PRS_CONSUMER_WDOG0_SRC1 - WDOG0 SRC1 Consumer Selection ......377

13. GPCRC - General Purpose Cyclic Redundancy Check ..............378

13.1 Introduction..............................378

13.2 Features ..............................378

13.3 Functional Description ..........................379

13.3.1 Polynomial Specification ........................380

13.3.2 Input and Output Specification ......................380

13.3.3 Initialization ............................380

13.3.4 DMA Usage ............................380

13.3.5 Byte-Level Bit Reversal and Byte Reordering .................381

13.4 GPCRC Register Map ..........................384

13.5 GPCRC Register Description ........................385

13.5.1 GPCRC_IPVERSION - IP Version ID ...................385

silabs.com

| Building a more connected world. Rev. 1.0 | 9

13.5.2 GPCRC_EN - CRC Enable .......................386

13.5.3 GPCRC_CTRL - Control Register .....................387

13.5.4 GPCRC_CMD - Command Register ....................388

13.5.5 GPCRC_INIT - CRC Init Value ......................388

13.5.6 GPCRC_POLY - CRC Polynomial Value ..................389

13.5.7 GPCRC_INPUTDATA - Input 32-Bit Data Register ...............389

13.5.8 GPCRC_INPUTDATAHWORD - Input 16-Bit Data Register ............390

13.5.9 GPCRC_INPUTDATABYTE - Input 8-Bit Data Register .............390

13.5.10 GPCRC_DATA - CRC Data Register ...................391

13.5.11 GPCRC_DATAREV - CRC Data Reverse Register ..............391

13.5.12 GPCRC_DATABYTEREV - CRC Data Byte Reverse Register ...........392

14. RTCC - Real Time Clock with Capture.....................393

14.1 Introduction..............................393

14.2 Features ..............................393

14.3 Functional Description ..........................394

14.3.1 RTCC Counter ...........................395

14.3.2 Capture/Compare Channels ......................397

14.3.3 Interrupts and PRS Output .......................398

14.3.4 Register Lock ...........................399

14.3.5 Programmer's Model .........................399

14.3.6 Debug Features and Description .....................399

14.4 RTCC Register Map ...........................400

14.5 RTCC Register Description ........................402

14.5.1 RTCC_IPVERSION - IP VERSION ....................402

14.5.2 RTCC_EN - Module Enable Register ...................402

14.5.3 RTCC_CFG - Configuration Register ...................403

14.5.4 RTCC_CMD - Command Register ....................404

14.5.5 RTCC_STATUS - Status Register ....................405

14.5.6 RTCC_IF - RTCC Interrupt Flags .....................406

14.5.7 RTCC_IEN - Interrupt Enable Register ...................407

14.5.8 RTCC_PRECNT - Pre-Counter Value Register ................408

14.5.9 RTCC_CNT - Counter Value Register ...................408

14.5.10 RTCC_COMBCNT - Combined Pre-Counter and Counter Valu... ..........409

14.5.11 RTCC_SYNCBUSY - Synchronization Busy Register ..............409

14.5.12 RTCC_LOCK - Configuration Lock Register .................410

14.5.13 RTCC_CCx_CTRL - CC Channel Control Register ..............411

14.5.14 RTCC_CCx_OCVALUE - Output Compare Value Register ............412

14.5.15 RTCC_CCx_ICVALUE - Input Capture Value Register .............412

15. BURTC - Back-Up Real Time Counter .....................413

15.1 Introduction..............................413

15.2 Features ..............................413

15.3 Functional Description ..........................414

15.3.1 Clock Selection ...........................414

15.3.2 Configuration ...........................414

15.3.3 Debug Features and Description .....................414

silabs.com

| Building a more connected world. Rev. 1.0 | 10

15.3.4 Counter .............................415

15.3.5 Compare Channel ..........................415

15.3.6 Interrupts .............................416

15.3.7 Register Lock ...........................416

15.4 BURTC Register Map ..........................417

15.5 BURTC Register Description ........................418

15.5.1 BURTC_IPVERSION - IP Version ID....................418

15.5.2 BURTC_EN - Module Enable Register ...................419

15.5.3 BURTC_CFG - Configuration Register ...................420

15.5.4 BURTC_CMD - Command Register ....................421

15.5.5 BURTC_STATUS - Status Register ....................422

15.5.6 BURTC_IF - Interrupt Flag Register ....................422

15.5.7 BURTC_IEN - Interrupt Enable Register ..................423

15.5.8 BURTC_PRECNT - Pre-Counter Value Register ................423

15.5.9 BURTC_CNT - Counter Value Register ...................424

15.5.10 BURTC_EM4WUEN - EM4 Wakeup Request Enable Register ..........424

15.5.11 BURTC_SYNCBUSY - Synchronization Busy Register .............425

15.5.12 BURTC_LOCK - Configuration Lock Register ................426

15.5.13 BURTC_COMP - Compare Value Register .................426

16. BURAM - Backup RAM ..........................427

16.1 Introduction..............................427

16.2 Functional Description ..........................427

16.3 BURAM Register Map ..........................427

16.4 BURAM Register Description ........................428

16.4.1 BURAM_RETx_REG - Retention Register ..................428

17. LETIMER - Low Energy Timer ........................429

17.1 Introduction..............................429

17.2 Features ..............................429

17.3 Functional Description ..........................430

17.3.1 Internal Overview ..........................431

17.3.2 Free Running Mode .........................432

17.3.3 One-shot Mode ...........................433

17.3.4 Buffered Mode ...........................434

17.3.5 Double Mode ...........................435

17.4 Clock Frequency ............................436

17.5 PRS Input Triggers ...........................437

17.6 Debug ...............................437

17.7 Output Action .............................438

17.8 PRS Output .............................438

17.9 Interrupts ..............................438

17.10 Using the LETIMER in EM3 ........................438

17.11 Register Access............................438

silabs.com

| Building a more connected world. Rev. 1.0 | 11

17.12 Programmer's Model ..........................439

17.12.1 FREE Running Mode ........................440

17.12.2 One Shot Mode ..........................441

17.12.3 DOUBLE Mode ..........................441

17.12.4 BUFFERED Mode .........................442

17.12.5 Continuous Output Generation .....................443

17.12.6 PWM Output ...........................444

17.13 LETIMER Register Map .........................445

17.14 LETIMER Register Description .......................447

17.14.1 LETIMER_IPVERSION - IP Version ...................447

17.14.2 LETIMER_EN - Module En ......................447

17.14.3 LETIMER_CTRL - Control Register ....................448

17.14.4 LETIMER_CMD - Command Register ...................450

17.14.5 LETIMER_STATUS - Status Register ...................451

17.14.6 LETIMER_CNT - Counter Value Register..................451

17.14.7 LETIMER_COMP0 - Compare Value Register 0 ...............452

17.14.8 LETIMER_COMP1 - Compare Value Register 1 ...............452

17.14.9 LETIMER_TOP - Counter TOP Value Register ................453

17.14.10 LETIMER_TOPBUFF - Buffered Counter TOP Value .............453

17.14.11 LETIMER_REP0 - Repeat Counter Register 0................454

17.14.12 LETIMER_REP1 - Repeat Counter Register 1................454

17.14.13 LETIMER_IF - Interrupt Flag Register ..................455

17.14.14 LETIMER_IEN - Interrupt Enable Register .................456

17.14.15 LETIMER_SYNCBUSY - Synchronization Busy Register ............457

17.14.16 LETIMER_PRSMODE - PRS Input Mode Select Register ............458

18. TIMER - Timer/Counter ..........................460

18.1 Introduction..............................460

18.2 Features ..............................461

18.3 Functional Description ..........................462

18.3.1 Register Access...........................462

18.3.2 Counter Modes ...........................463

18.3.3 Compare/Capture Channels ......................469

18.3.4 Dead-Time Insertion Unit .......................479

18.3.5 Debug Mode ............................483

18.3.6 Interrupts, DMA and PRS Output .....................483

18.3.7 GPIO Input/Output ..........................483

18.4 TIMER Register Map ..........................484

18.5 TIMER Register Description ........................487

18.5.1 TIMER_IPVERSION - IP Version ID ....................487

18.5.2 TIMER_CFG - Configuration Register ...................488

18.5.3 TIMER_CTRL - Control Register .....................491

18.5.4 TIMER_CMD - Command Register ....................492

18.5.5 TIMER_STATUS - Status Register ....................493

18.5.6 TIMER_IF - Interrupt Flag Register ....................496

18.5.7 TIMER_IEN - Interrupt Enable Register ...................498

18.5.8 TIMER_TOP - Counter Top Value Register .................499

silabs.com

| Building a more connected world. Rev. 1.0 | 12

18.5.9 TIMER_TOPB - Counter Top Value Buffer Register ...............499

18.5.10 TIMER_CNT - Counter Value Register ..................500

18.5.11 TIMER_LOCK - TIMER Configuration Lock Register ..............500

18.5.12 TIMER_EN - Module En .......................501

18.5.13 TIMER_CCx_CFG - CC Channel Configuration Register ............502

18.5.14 TIMER_CCx_CTRL - CC Channel Control Register ..............504

18.5.15 TIMER_CCx_OC - OC Channel Value Register ...............505

18.5.16 TIMER_CCx_OCB - OC Channel Value Buffer Register .............506

18.5.17 TIMER_CCx_ICF - IC Channel Value Register ................506

18.5.18 TIMER_CCx_ICOF - IC Channel Value Overflow Register ............506

18.5.19 TIMER_DTCFG - DTI Configuration Register ................507

18.5.20 TIMER_DTTIMECFG - DTI Time Configuration Register ............508

18.5.21 TIMER_DTFCFG - DTI Fault Configuration Register ..............509

18.5.22 TIMER_DTCTRL - DTI Control Register ..................510

18.5.23 TIMER_DTOGEN - DTI Output Generation Enable Register ...........511

18.5.24 TIMER_DTFAULT - DTI Fault Register ..................512

18.5.25 TIMER_DTFAULTC - DTI Fault Clear Register ................513

18.5.26 TIMER_DTLOCK - DTI Configuration Lock Register ..............514

19. PDM - PDM Interface ...........................515

19.1 Introduction..............................515

19.2 Features ..............................516

19.3 Functional Description ..........................516

19.3.1 Overview .............................517

19.3.2 PDM Clock Generation ........................517

19.3.3 Filter Order ............................517

19.3.4 Down Sample Rate .........................518

19.3.5 Multi Channel Operation ........................518

19.3.6 Output Options ...........................518

19.3.7 FIFO ..............................518

19.3.8 DMA Support ...........................519

19.3.9 PRS Support ............................519

19.3.10 PDM Energy Modes .........................519

19.3.11 Debug Mode ...........................519

19.3.12 Pin Configurations .........................519

19.3.13 Programmer's Model.........................520

19.4 Applications .............................522

19.4.1 PDM Microphones ..........................522

19.4.2 Isolated Sigma Delta Modulators .....................523

19.5 PDM Register Map ...........................524

19.6 PDM Register Description .........................525

19.6.1 PDM_IPVERSION - IP Version ID ....................525

19.6.2 PDM_EN - PDM Module Enable Register ..................526

19.6.3 PDM_CTRL - PDM Core Control Register ..................526

19.6.4 PDM_CMD - PDM Core Command Register .................527

19.6.5 PDM_STATUS - PDM Status Register ...................528

19.6.6 PDM_CFG0 - PDM Core Configuration Register0 ...............529

silabs.com

| Building a more connected world. Rev. 1.0 | 13

19.6.7 PDM_CFG1 - PDM Core Configuration Register1 ...............531

19.6.8 PDM_RXDATA - PDM Received Data Register ................531

19.6.9 PDM_IF - Interrupt Flag Register .....................532

19.6.10 PDM_IEN - Interrupt Flag Register ....................532

19.6.11 PDM_SYNCBUSY - Synchronization Busy Register ..............533

20. USART - Universal Synchronous Asynchronous Receiver/Transmitter ........534

20.1 Introduction..............................534

20.2 Features ..............................535

20.3 Functional Description ..........................536

20.3.1 Modes of Operation .........................537

20.3.2 Asynchronous Operation ........................537

20.3.3 Synchronous Operation ........................553

20.3.4 Hardware Flow Control ........................559

20.3.5 Debug Halt ............................559

20.3.6 PRS-triggered Transmissions ......................559

20.3.7 PRS RX Input ...........................559

20.3.8 PRS CLK Input ...........................560

20.3.9 DMA Support ...........................560

20.3.10 Timer ..............................561

20.3.11 Interrupts ............................566

20.3.12 IrDA Modulator/ Demodulator ......................567

20.4 USART Register Map ..........................568

20.5 USART Register Description ........................571

20.5.1 USART_IPVERSION - IPVERSION ....................571

20.5.2 USART_EN - USART Enable ......................571

20.5.3 USART_CTRL - Control Register .....................572

20.5.4 USART_FRAME - USART Frame Format Register ...............577

20.5.5 USART_TRIGCTRL - USART Trigger Control Register .............579

20.5.6 USART_CMD - Command Register ....................580

20.5.7 USART_STATUS - USART Status Register .................581

20.5.8 USART_CLKDIV - Clock Control Register ..................582

20.5.9 USART_RXDATAX - RX Buffer Data Extended Register .............583

20.5.10 USART_RXDATA - RX Buffer Data Register ................583

20.5.11 USART_RXDOUBLEX - RX Buffer Double Data Extended Register .........584

20.5.12 USART_RXDOUBLE - RX FIFO Double Data Register .............585

20.5.13 USART_RXDATAXP - RX Buffer Data Extended Peek Register ..........585

20.5.14 USART_RXDOUBLEXP - RX Buffer Double Data Extended Peek R... ........586

20.5.15 USART_TXDATAX - TX Buffer Data Extended Register .............587

20.5.16 USART_TXDATA - TX Buffer Data Register .................588

20.5.17 USART_TXDOUBLEX - TX Buffer Double Data Extended Register .........589

20.5.18 USART_TXDOUBLE - TX Buffer Double Data Register .............590

20.5.19 USART_IF - Interrupt Flag Register....................591

20.5.20 USART_IEN - Interrupt Enable Register ..................593

20.5.21 USART_IRCTRL - IrDA Control Register ..................594

20.5.22 USART_I2SCTRL - I2S Control Register ..................595

20.5.23 USART_TIMING - Timing Register ....................597

silabs.com

| Building a more connected world. Rev. 1.0 | 14

20.5.24 USART_CTRLX - Control Register Extended ................599

20.5.25 USART_TIMECMP0 - Used to Generate Interrupts and Vario... ..........601

20.5.26 USART_TIMECMP1 - Used to Generate Interrupts and Vario... ..........603

20.5.27 USART_TIMECMP2 - Used to Generate Interrupts and Vario... ..........605

21. EUART - Enhanced Universal Asynchronous Receiver/Transmitter .........607

21.1 Introduction..............................607

21.2 Features ..............................608

21.3 Functional Description ..........................609

21.3.1 Modes of Operation .........................609

21.3.2 Frame Format ...........................610

21.3.3 Parity Bit Calculation and Handling ....................611

21.3.4 Clock Generation ..........................612

21.3.5 Auto Baud Detection .........................613

21.3.6 Data Transmission ..........................614

21.3.7 Transmit FIFO Operation .......................615

21.3.8 Frame Transmission Control ......................616

21.3.9 Transmission Delay .........................616

21.3.10 Data Reception ..........................616

21.3.11 Receive FIFO Operation .......................617

21.3.12 Blocking Incoming Data........................618

21.3.13 Data Sampling and Filtering ......................619

21.3.14 Parity Error ............................620

21.3.15 Framing Error and Break Detection ....................620

21.3.16 Programmable Start Frame ......................621

21.3.17 Programmable Signal Frame ......................621

21.3.18 Local Loopback ..........................621

21.3.19 Half Duplex Communication ......................621

21.3.20 Single Data-link ..........................622

21.3.21 Single Data-link with External Driver ...................622

21.3.22 Two Data-links ...........................622

21.3.23 Multi-Processor Mode ........................623

21.3.24 Collision Detection .........................623

21.3.25 Hardware Flow Control ........................623

21.3.26 Debug Halt ............................624

21.3.27 PRS-triggered Transmissions......................624

21.3.28 PRS RX Input ...........................624

21.3.29 DMA Support ...........................624

21.3.30 Interrupts ............................625

21.3.31 EM2 Operation (LF Mode Only) .....................625

21.3.32 IrDA Modulator/ Demodulator ......................626

21.4 EUSART Register Map ..........................627

21.5 EUSART Register Description .......................629

21.5.1 EUSART_IPVERSION - IP Version ID ...................629

21.5.2 EUSART_EN - Enable Register .....................630

21.5.3 EUSART_CFG0 - Configuration 0 Register .................631

21.5.4 EUSART_CFG1 - Configuration 1 Register .................634

silabs.com

| Building a more connected world. Rev. 1.0 | 15

21.5.5 EUSART_FRAMECFG - Frame Format Register ...............637

21.5.6 EUSART_IRHFCFG - HF IrDA Mod Config Register ..............638

21.5.7 EUSART_IRLFCFG - LF IrDA Pulse Config Register ..............639

21.5.8 EUSART_TIMINGCFG - Timing Register ..................639

21.5.9 EUSART_STARTFRAMECFG - Start Frame Register ..............640

21.5.10 EUSART_SIGFRAMECFG - Signal Frame Register ..............640

21.5.11 EUSART_CLKDIV - Clock Divider Register .................641

21.5.12 EUSART_TRIGCTRL - Trigger Control Register ...............641

21.5.13 EUSART_CMD - Command Register ...................642

21.5.14 EUSART_RXDATA - RX Data Register ..................643

21.5.15 EUSART_RXDATAP - RX Data Peek Register ................643

21.5.16 EUSART_TXDATA - TX Data Register ..................644

21.5.17 EUSART_STATUS - Status Register ...................645

21.5.18 EUSART_IF - Interrupt Flag Register ...................647

21.5.19 EUSART_IEN - Interrupt Enable Register .................649

21.5.20 EUSART_SYNCBUSY - Synchronization Busy Register .............651

22. I2C - Inter-Integrated Circuit Interface .....................653

22.1 Introduction..............................653

22.2 Features ..............................653

22.3 Functional Description ..........................654

22.3.1 I2C-Bus Overview ..........................655

22.3.2 Enable and Reset ..........................659

22.3.3 Pin Configuration ..........................659

22.3.4 Safely Disabling and Changing Slave Configuration...............659

22.3.5 Clock Generation ..........................660

22.3.6 Arbitration .............................660

22.3.7 Buffers ..............................660

22.3.8 Master Operation ..........................663

22.3.9 Bus States ............................671

22.3.10 Slave Operation ..........................671

22.3.11 Transfer Automation .........................675

22.3.12 Using 10-bit Addresses ........................676

22.3.13 Error Handling ...........................676

22.3.14 DMA Support ...........................678

22.3.15 Interrupts ............................678

22.3.16 Wake-up .............................678

22.4 I2C Register Map............................679

22.5 I2C Register Description .........................681

22.5.1 I2C_IPVERSION - IP VERSION Register ..................681

22.5.2 I2C_EN - Enable Register .......................681

22.5.3 I2C_CTRL - Control Register ......................682

22.5.4 I2C_CMD - Command Register .....................686

22.5.5 I2C_STATE - State Register ......................687

22.5.6 I2C_STATUS - Status Register .....................688

22.5.7 I2C_CLKDIV - Clock Division Register ...................689

22.5.8 I2C_SADDR - Slave Address Register ...................689

silabs.com

| Building a more connected world. Rev. 1.0 | 16

22.5.9 I2C_SADDRMASK - Slave Address Mask Register ...............690

22.5.10 I2C_RXDATA - Receive Buffer Data Register ................690

22.5.11 I2C_RXDOUBLE - Receive Buffer Double Data Register ............691

22.5.12 I2C_RXDATAP - Receive Buffer Data Peek Register ..............691

22.5.13 I2C_RXDOUBLEP - Receive Buffer Double Data Peek Register ..........692

22.5.14 I2C_TXDATA - Transmit Buffer Data Register ................692

22.5.15 I2C_TXDOUBLE - Transmit Buffer Double Data Register ............693

22.5.16 I2C_IF - Interrupt Flag Register .....................694

22.5.17 I2C_IEN - Interrupt Enable Register ...................696

23. IADC - Incremental Analog to Digital Converter .................698

23.1 Introduction..............................698

23.2 Features ..............................699

23.3 Functional Description ..........................700

23.3.1 Register Access...........................701

23.3.2 Clocking .............................702

23.3.3 Conversion Timing ..........................703

23.3.4 Reference Selection and Analog Gain ...................710

23.3.5 Input and Configuration Selection .....................710

23.3.6 Gain and Offset Correction .......................715

23.3.7 Output Data FIFOs ..........................719

23.3.8 Window Compare ..........................722

23.3.9 Interrupts .............................723

23.4 IADC Register Map ...........................724

23.5 IADC Register Description.........................727

23.5.1 IADC_IPVERSION - IPVERSION .....................727

23.5.2 IADC_EN - Enable ..........................727

23.5.3 IADC_CTRL - Control .........................728

23.5.4 IADC_CMD - Command ........................730

23.5.5 IADC_TIMER - Timer .........................731

23.5.6 IADC_STATUS - Status ........................732

23.5.7 IADC_MASKREQ - Mask Request ....................733

23.5.8 IADC_STMASK - Scan Table Mask ....................734

23.5.9 IADC_CMPTHR - Digital Window Comparator Threshold .............734

23.5.10 IADC_IF - Interrupt Flags .......................735

23.5.11 IADC_IEN - Interrupt Enable ......................737

23.5.12 IADC_TRIGGER - Trigger .......................739

23.5.13 IADC_CFGx - Configuration ......................742

23.5.14 IADC_SCALEx - Scaling .......................744

23.5.15 IADC_SCHEDx - Scheduling ......................744

23.5.16 IADC_SINGLEFIFOCFG - Single FIFO Configuration .............745

23.5.17 IADC_SINGLEFIFODATA - Single FIFO Read Data ..............746

23.5.18 IADC_SINGLEFIFOSTAT - Single FIFO Status ................746

23.5.19 IADC_SINGLEDATA - Single Data ....................747

23.5.20 IADC_SCANFIFOCFG - Scan FIFO Configuration ...............748

23.5.21 IADC_SCANFIFODATA - Scan FIFO Read Data ...............749

23.5.22 IADC_SCANFIFOSTAT - Scan FIFO Status .................749

silabs.com

| Building a more connected world. Rev. 1.0 | 17

23.5.23 IADC_SCANDATA - Scan Data .....................750

23.5.24 IADC_SINGLE - Single Queue Port Selection ................751

23.5.25 IADC_SCANx - SCAN Entry ......................753

24. GPIO - General Purpose Input/Output .....................755

24.1 Introduction .............................755

24.2 Features ..............................756

24.3 Functional Description ..........................757

24.3.1 Pin Configuration ..........................758

24.3.2 Alternate Port Control ........................760

24.3.3 Slew Rate .............................760

24.3.4 Input Disable ............................760

24.3.5 Configuration Lock ..........................760

24.3.6 EM2 Functionality ..........................760

24.3.7 EM4 Functionality ..........................760

24.3.8 EM4 Wakeup ...........................761

24.3.9 Debug Connections .........................761

24.3.10 Interrupt Generation .........................762

24.3.11 Output to PRS ...........................763

24.3.12 Peripheral Resource Routing ......................763

24.4 Synchronization ............................768

24.5 GPIO Register Map ...........................769

24.6 GPIO Register Description ........................786

24.6.1 GPIO_PORTA_CTRL - Port Control ....................786

24.6.2 GPIO_PORTA_MODEL - Mode Low ....................787

24.6.3 GPIO_PORTA_MODEH - Mode High ...................792

24.6.4 GPIO_PORTA_DOUT - Data Out .....................793

24.6.5 GPIO_PORTA_DIN - Data in ......................793

24.6.6 GPIO_PORTB_CTRL - Port Control ....................794

24.6.7 GPIO_PORTB_MODEL - Mode Low ....................795

24.6.8 GPIO_PORTB_DOUT - Data Out .....................798

24.6.9 GPIO_PORTB_DIN - Data in ......................798

24.6.10 GPIO_PORTC_CTRL - Port Control ...................799

24.6.11 GPIO_PORTC_MODEL - Mode Low ...................800

24.6.12 GPIO_PORTC_DOUT - Data Out ....................805

24.6.13 GPIO_PORTC_DIN - Data in ......................805

24.6.14 GPIO_PORTD_CTRL - Port Control ...................806

24.6.15 GPIO_PORTD_MODEL - Mode Low ...................807

24.6.16 GPIO_PORTD_DOUT - Data Out ....................809

24.6.17 GPIO_PORTD_DIN - Data in ......................810

24.6.18 GPIO_LOCK - Lock Register ......................810

24.6.19 GPIO_GPIOLOCKSTATUS - Lock Status .................811

24.6.20 GPIO_ABUSALLOC - A Bus Allocation ..................812

24.6.21 GPIO_BBUSALLOC - B Bus Allocation ..................814

24.6.22 GPIO_CDBUSALLOC - CD Bus Allocation .................816

24.6.23 GPIO_EXTIPSELL - External Interrupt Port Select Low .............818

24.6.24 GPIO_EXTIPSELH - External Interrupt Port Select High .............821

silabs.com

| Building a more connected world. Rev. 1.0 | 18

24.6.25 GPIO_EXTIPINSELL - External Interrupt Pin Select Low ............823

24.6.26 GPIO_EXTIPINSELH - External Interrupt Pin Select High ............826

24.6.27 GPIO_EXTIRISE - External Interrupt Rising Edge Trigger ............827

24.6.28 GPIO_EXTIFALL - External Interrupt Falling Edge Trigger ............828

24.6.29 GPIO_IF - Interrupt Flag .......................829

24.6.30 GPIO_IEN - Interrupt Enable ......................831

24.6.31 GPIO_EM4WUEN - EM4 Wakeup Enable .................833

24.6.32 GPIO_EM4WUPOL - EM4 Wakeup Polarity .................833

24.6.33 GPIO_DBGROUTEPEN - Debugger Route Pin Enable .............834

24.6.34 GPIO_TRACEROUTEPEN - Trace Route Pin Enable .............835

24.6.35 GPIO_CMU_ROUTEEN - CMU Pin Enable .................836

24.6.36 GPIO_CMU_CLKIN0ROUTE - CLKIN0 Port/Pin Select .............836

24.6.37 GPIO_CMU_CLKOUT0ROUTE - CLKOUT0 Port/Pin Select ...........837

24.6.38 GPIO_CMU_CLKOUT1ROUTE - CLKOUT1 Port/Pin Select ...........837

24.6.39 GPIO_CMU_CLKOUT2ROUTE - CLKOUT2 Port/Pin Select ...........838

24.6.40 GPIO_DCDC_ROUTEEN - DCDC Pin Enable ................838

24.6.41 GPIO_I2C0_ROUTEEN - I2C0 Pin Enable .................839

24.6.42 GPIO_I2C0_SCLROUTE - SCL Port/Pin Select ...............839

24.6.43 GPIO_I2C0_SDAROUTE - SDA Port/Pin Select ...............840

24.6.44 GPIO_I2C1_ROUTEEN - I2C1 Pin Enable .................840

24.6.45 GPIO_I2C1_SCLROUTE - SCL Port/Pin Select ...............841

24.6.46 GPIO_I2C1_SDAROUTE - SDA Port/Pin Select ...............841

24.6.47 GPIO_LETIMER0_ROUTEEN - LETIMER Pin Enable .............842

24.6.48 GPIO_LETIMER0_OUT0ROUTE - OUT0 Port/Pin Select ............842

24.6.49 GPIO_LETIMER0_OUT1ROUTE - OUT1 Port/Pin Select ............843

24.6.50 GPIO_EUART0_ROUTEEN - EUART Pin Enable ...............843

24.6.51 GPIO_EUART0_CTSROUTE - CTS Port/Pin Select ..............844

24.6.52 GPIO_EUART0_RTSROUTE - RTS Port/Pin Select ..............844

24.6.53 GPIO_EUART0_RXROUTE - RX Port/Pin Select ...............845

24.6.54 GPIO_EUART0_TXROUTE - TX Port/Pin Select ...............845

24.6.55 GPIO_PDM_ROUTEEN - PDM Pin Enable .................846

24.6.56 GPIO_PDM_CLKROUTE - CLK Port/Pin Select ...............846

24.6.57 GPIO_PDM_DAT0ROUTE - DAT0 Port/Pin Select ..............847

24.6.58 GPIO_PDM_DAT1ROUTE - DAT1 Port/Pin Select ..............847

24.6.59 GPIO_PRS0_ROUTEEN - PRS0 Pin Enable ................848

24.6.60 GPIO_PRS0_ASYNCH0ROUTE - ASYNCH0 Port/Pin Select ...........849

24.6.61 GPIO_PRS0_ASYNCH1ROUTE - ASYNCH1 Port/Pin Select ...........850

24.6.62 GPIO_PRS0_ASYNCH2ROUTE - ASYNCH2 Port/Pin Select ...........850

24.6.63 GPIO_PRS0_ASYNCH3ROUTE - ASYNCH3 Port/Pin Select ...........851

24.6.64 GPIO_PRS0_ASYNCH4ROUTE - ASYNCH4 Port/Pin Select ...........851

24.6.65 GPIO_PRS0_ASYNCH5ROUTE - ASYNCH5 Port/Pin Select ...........852

24.6.66 GPIO_PRS0_ASYNCH6ROUTE - ASYNCH6 Port/Pin Select ...........852

24.6.67 GPIO_PRS0_ASYNCH7ROUTE - ASYNCH7 Port/Pin Select ...........853

24.6.68 GPIO_PRS0_ASYNCH8ROUTE - ASYNCH8 Port/Pin Select ...........853

24.6.69 GPIO_PRS0_ASYNCH9ROUTE - ASYNCH9 Port/Pin Select ...........854

24.6.70 GPIO_PRS0_ASYNCH10ROUTE - ASYNCH10 Port/Pin Select ..........854

24.6.71 GPIO_PRS0_ASYNCH11ROUTE - ASYNCH11 Port/Pin Select ..........855

24.6.72 GPIO_PRS0_SYNCH0ROUTE - SYNCH0 Port/Pin Select ............855

silabs.com

| Building a more connected world. Rev. 1.0 | 19

24.6.73 GPIO_PRS0_SYNCH1ROUTE - SYNCH1 Port/Pin Select ............856

24.6.74 GPIO_PRS0_SYNCH2ROUTE - SYNCH2 Port/Pin Select ............856

24.6.75 GPIO_PRS0_SYNCH3ROUTE - SYNCH3 Port/Pin Select ............857

24.6.76 GPIO_TIMER0_ROUTEEN - TIMER0 Pin Enable ...............858

24.6.77 GPIO_TIMER0_CC0ROUTE - CC0 Port/Pin Select ..............859

24.6.78 GPIO_TIMER0_CC1ROUTE - CC1 Port/Pin Select ..............859

24.6.79 GPIO_TIMER0_CC2ROUTE - CC2 Port/Pin Select ..............860

24.6.80 GPIO_TIMER0_CDTI0ROUTE - CDTI0 Port/Pin Select .............860

24.6.81 GPIO_TIMER0_CDTI1ROUTE - CDTI1 Port/Pin Select .............861

24.6.82 GPIO_TIMER0_CDTI2ROUTE - CDTI2 Port/Pin Select .............861

24.6.83 GPIO_TIMER1_ROUTEEN - TIMER1 Pin Enable ...............862

24.6.84 GPIO_TIMER1_CC0ROUTE - CC0 Port/Pin Select ..............863

24.6.85 GPIO_TIMER1_CC1ROUTE - CC1 Port/Pin Select ..............863

24.6.86 GPIO_TIMER1_CC2ROUTE - CC2 Port/Pin Select ..............864

24.6.87 GPIO_TIMER1_CDTI0ROUTE - CDTI0 Port/Pin Select .............864

24.6.88 GPIO_TIMER1_CDTI1ROUTE - CDTI1 Port/Pin Select .............865

24.6.89 GPIO_TIMER1_CDTI2ROUTE - CDTI2 Port/Pin Select .............865

24.6.90 GPIO_TIMER2_ROUTEEN - TIMER2 Pin Enable ...............866

24.6.91 GPIO_TIMER2_CC0ROUTE - CC0 Port/Pin Select ..............867

24.6.92 GPIO_TIMER2_CC1ROUTE - CC1 Port/Pin Select ..............867

24.6.93 GPIO_TIMER2_CC2ROUTE - CC2 Port/Pin Select ..............868

24.6.94 GPIO_TIMER2_CDTI0ROUTE - CDTI0 Port/Pin Select .............868

24.6.95 GPIO_TIMER2_CDTI1ROUTE - CDTI1 Port/Pin Select .............869

24.6.96 GPIO_TIMER2_CDTI2ROUTE - CDTI2 Port/Pin Select .............869

24.6.97 GPIO_TIMER3_ROUTEEN - TIMER3 Pin Enable ...............870

24.6.98 GPIO_TIMER3_CC0ROUTE - CC0 Port/Pin Select ..............871

24.6.99 GPIO_TIMER3_CC1ROUTE - CC1 Port/Pin Select ..............871

24.6.100 GPIO_TIMER3_CC2ROUTE - CC2 Port/Pin Select ..............872

24.6.101 GPIO_TIMER3_CDTI0ROUTE - CDTI0 Port/Pin Select ............872

24.6.102 GPIO_TIMER3_CDTI1ROUTE - CDTI1 Port/Pin Select ............873

24.6.103 GPIO_TIMER3_CDTI2ROUTE - CDTI2 Port/Pin Select ............873

24.6.104 GPIO_TIMER4_ROUTEEN - TIMER4 Pin Enable ..............874

24.6.105 GPIO_TIMER4_CC0ROUTE - CC0 Port/Pin Select ..............875

24.6.106 GPIO_TIMER4_CC1ROUTE - CC1 Port/Pin Select ..............875

24.6.107 GPIO_TIMER4_CC2ROUTE - CC2 Port/Pin Select ..............876

24.6.108 GPIO_TIMER4_CDTI0ROUTE - CDTI0 Port/Pin Select ............876

24.6.109 GPIO_TIMER4_CDTI1ROUTE - CDTI1 Port/Pin Select ............877

24.6.110 GPIO_TIMER4_CDTI2ROUTE - CDTI2 Port/Pin Select ............877

24.6.111 GPIO_USART0_ROUTEEN - USART0 Pin Enable ..............878

24.6.112 GPIO_USART0_CSROUTE - CS Port/Pin Select ..............879

24.6.113 GPIO_USART0_CTSROUTE - CTS Port/Pin Select..............879

24.6.114 GPIO_USART0_RTSROUTE - RTS Port/Pin Select..............880

24.6.115 GPIO_USART0_RXROUTE - RX Port/Pin Select ..............880

24.6.116 GPIO_USART0_CLKROUTE - SCLK Port/Pin Select .............881

24.6.117 GPIO_USART0_TXROUTE - TX Port/Pin Select ...............881

24.6.118 GPIO_USART1_ROUTEEN - USART1 Pin Enable ..............882

24.6.119 GPIO_USART1_CSROUTE - CS Port/Pin Select ..............883

24.6.120 GPIO_USART1_CTSROUTE - CTS Port/Pin Select..............883

silabs.com

| Building a more connected world. Rev. 1.0 | 20

/