Intel LXD972M User manual

- Category

- Network transceiver modules

- Type

- User manual

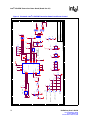

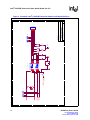

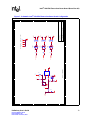

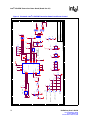

Intel LXD972M is a single-port 10/100 Mbps PHY transceiver that supports 3.3V operation and has an optional 2.5V I/O voltage. It consumes only 300 mW of power, has low power consumption, and features LED indicators for major functions. With its configurable settings and JTAG boundary scan port, this device is suitable for various applications.

Intel LXD972M is a single-port 10/100 Mbps PHY transceiver that supports 3.3V operation and has an optional 2.5V I/O voltage. It consumes only 300 mW of power, has low power consumption, and features LED indicators for major functions. With its configurable settings and JTAG boundary scan port, this device is suitable for various applications.

-

1

1

-

2

2

-

3

3

-

4

4

-

5

5

-

6

6

-

7

7

-

8

8

-

9

9

-

10

10

-

11

11

-

12

12

-

13

13

-

14

14

-

15

15

-

16

16

-

17

17

-

18

18

-

19

19

-

20

20

-

21

21

-

22

22

Intel LXD972M User manual

- Category

- Network transceiver modules

- Type

- User manual

Intel LXD972M is a single-port 10/100 Mbps PHY transceiver that supports 3.3V operation and has an optional 2.5V I/O voltage. It consumes only 300 mW of power, has low power consumption, and features LED indicators for major functions. With its configurable settings and JTAG boundary scan port, this device is suitable for various applications.

Ask a question and I''ll find the answer in the document

Finding information in a document is now easier with AI

Related papers

Other documents

-

ST STM32F107 series User manual

-

Conceptronic C31-278 Datasheet

-

Detecto 225 SnapStream Quick start guide

-

Texas Instruments DP83620 Ethernet Physical Layer Transceiver Demo Board User guide

-

Extron DTP3 R 301 User manual

-

Altera tPad DE2-115 User manual

-

Terasic VEEK-MT User manual

-

Extron DTP2 R 211 User manual

-

Freescale Semiconductor MPC5777C EVB User manual

-

Extron DTP3 T 202 User manual