®

DB14-000165-01

LSI53C875/875E

PCI to Ultra SCSI

I/O Processor

TECHNICAL

MANUAL

April 2003

Version 4.2

ii

This document contains proprietary information of LSI Logic Corporation. The

information contained herein is not to be used by or disclosed to third parties

without the express written permission of an officer of LSI Logic Corporation.

LSI Logic products are not intended for use in life-support appliances, devices,

or systems. Use of any LSI Logic product in such applications without written

consent of the appropriate LSI Logic officer is prohibited.

Document DB14-000165-01, Sixth Edition (April 2003)

This document describes the LSI Logic LSI53C875/875E PCI to Ultra SCSI I/O

Processor and will remain the official reference source for all revisions/releases

of this product until rescinded by an update.

To receive product literature, visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein

at any time without notice. LSI Logic does not assume any responsibility or

liability arising out of the application or use of any product described herein,

except as expressly agreed to in writing by LSI Logic; nor does the purchase or

use of a product from LSI Logic convey a license under any patent rights,

copyrights, trademark rights, or any other of the intellectual property rights of

LSI Logic or third parties.

Copyright © 1998–2001/2003 by LSI Logic Corporation. All rights reserved.

TRADEMARK ACKNOWLEDGMENT

The LSI Logic logo design, TolerANT, SDMS, and SCRIPTS are registered

trademarks or trademarks of LSI Logic Corporation. All other brand and product

names may be trademarks of their respective companies.

Preface iii

Preface

This book is the primary reference and technical manual for the LSI Logic

LSI53C875/875E PCI to Ultra SCSI I/O Processor. It contains a complete

functional description for the LSI53C875/875E and includes complete

physical and electrical specifications for the LSI53C875/875E.

Audience

This technical manual is intended for system designers and programmers

who are using this device to design a SCSI port for PCI-based personal

computers, workstations, or embedded applications.

Organization

This document has the following chapters and appendixes:

• Chapter 1, General Description, includes general information about

the LSI53C875 and other members of the LSI53C8XX family of PCI

to SCSI I/O Processors.

• Chapter 2, Functional Description, describes the main functional

areas of the chip in more detail, including the interfaces to the SCSI

bus.

• Chapter 3, PCI Functional Description, describes the chip’s

connection to the PCI bus, including the PCI commands and

configuration registers supported.

• Chapter 4, Signal Descriptions, contains the pin diagrams and

definitions of each signal.

• Chapter 5, SCSI Operating Registers, describes each bit in the

operating registers, organized by address.

iv Preface

• Chapter 6, Instruction Set of the I/O Processor, defines all of the

SCSI SCRIPTS instructions that are supported by the LSI53C875.

• Chapter 7, Instruction Set of the I/O Processor, contains the

electrical characteristics and AC timings for the chip.

• Appendix A, Register Summary, is a register summary.

• Appendix B, External Memory Interface Diagram Examples,

contains several example interface drawings to connect the

LSI53C875 to an external ROM.

Related Publications

For background information, please contact:

ANSI

11 West 42nd Street

New York, NY 10036

(212) 642-4900

Ask for document number X3.131-199X (SCSI-2)

Global Engineering Documents

15 Inverness Way East

Englewood, CO 80112

(800) 854-7179 or (303) 397-7956 (outside U.S.) FAX (303) 397-2740

Ask for document number X3.131-1994 (SCSI-2); X3.253 (SCSI-3

Parallel Interface)

ENDL Publications

14426 Black Walnut Court

Saratoga, CA 95070

(408) 867-6642

Document names: SCSI Bench Reference, SCSI Encyclopedia, SCSI

Tutor

Prentice Hall

113 Sylvan Avenue

Englewood Cliffs, NJ 07632

(800) 947-7700

Ask for document number ISBN 0-13-796855-8, SCSI: Understanding

the Small Computer System Interface

Preface v

LSI Logic World Wide Web Home Page

www.lsilogic.com

SCSI SCRIPTS™ Processors Programming Guide, Version 2.2,

Order Number S14044.A

PCI Special Interest Group

2575 N. E. Katherine

Hillsboro, OR 97214

(800) 433-5177; (503) 693-6232 (International); FAX (503) 693-8344

Conventions Used in This Manual

The word assert means to drive a signal true or active. The word

deassert means to drive a signal false or inactive.

Hexadecimal numbers are indicated by the prefix “0x” —for example,

0x32CF. Binary numbers are indicated by the prefix “0b” —for example,

0b0011.0010.1100.1111.

Revision Record

Revision Date Remarks

1.0 6/95 Revision 1.0

2.0 3/96 Revision 2.0. Fast-20 changed to Ultra SCSI throughout.

3.0 9/96 Revision 3.0. Minor copy changes throughout.

4.0 2/98 Revision 4.0. Minor copy changes throughout

4.1 3/01 Product names changed from SYM to LSI.

4.2 4/03 Revision 4.2. Correct V

DD

-S in Table 4.3

vi Preface

Contents vii

Contents

Chapter 1 General Description

1.1 Package and Feature Options 1-4

1.2 Benefits of Ultra SCSI 1-4

1.3 TolerANT

®

Technology 1-5

1.4 LSI53C875 Benefits Summary 1-6

1.4.1 SCSI Performance 1-6

1.4.2 PCI Performance 1-7

1.4.3 Integration 1-7

1.4.4 Ease of Use 1-7

1.4.5 Flexibility 1-8

1.4.6 Reliability 1-9

1.4.7 Testability 1-9

Chapter 2 Functional Description

2.1 SCSI Functional Description 2-1

2.1.1 SCSI Core 2-1

2.1.2 DMA Core 2-2

2.1.3 SCRIPTS Processor 2-2

2.1.4 Internal SCRIPTS RAM 2-3

2.1.5 SDMS Software: The Total SCSI Solution 2-3

2.2 Designing an Ultra SCSI System 2-4

2.2.1 Using the SCSI Clock Doubler 2-4

2.3 Prefetching SCRIPTS Instructions 2-5

2.3.1 Opcode Fetch Burst Capability 2-6

2.4 External Memory Interface 2-6

2.5 PCI Cache Mode 2-8

2.5.1 Load/Store Instructions 2-8

2.5.2 3.3 V/5 V PCI Interface 2-9

2.5.3 Additional Access to General Purpose Pins 2-9

viii Contents

2.5.4 JTAG Boundary Scan Testing 2-10

2.5.5 Big and Little Endian Support 2-10

2.5.6 Loopback Mode 2-12

2.5.7 Parity Options 2-12

2.5.8 DMA FIFO 2-15

2.5.9 SCSI Bus Interface 2-19

2.5.10 Select/Reselect During Selection/Reselection 2-25

2.5.11 Synchronous Operation 2-25

2.5.12 Ultra SCSI Synchronous Data Transfers 2-27

2.5.13 Interrupt Handling 2-28

2.5.14 Chained Block Moves 2-34

2.6 Power Management 2-38

2.6.1 Power State D0 2-38

2.6.2 Power State D3 2-39

Chapter 3 PCI Functional Description

3.1 PCI Addressing 3-1

3.1.1 PCI Bus Commands and Functions Supported 3-2

3.2 PCI Cache Mode 3-4

3.2.1 Support for PCI Cache Line Size Register 3-4

3.2.2 Selection of Cache Line Size 3-5

3.2.3 Alignment 3-5

3.2.4 Memory Move Misalignment 3-6

3.2.5 Memory Write and Invalidate Command 3-6

3.2.6 Memory Read Line Command 3-8

3.2.7 Memory Read Multiple Command 3-9

3.3 Configuration Registers 3-11

Chapter 4 Signal Descriptions

4.1 MAD Bus Programming 4-22

Chapter 5 SCSI Operating Registers

Chapter 6 Instruction Set of the I/O Processor

6.1 SCSI SCRIPTS 6-1

6.1.1 Sample Operation 6-3

Contents ix

6.2 Block Move Instructions 6-5

6.2.1 First Dword 6-5

6.2.2 Second Dword 6-12

6.3 I/O Instruction 6-12

6.3.1 First Dword 6-12

6.3.2 Second Dword 6-21

6.4 Read/Write Instructions 6-21

6.4.1 First Dword 6-21

6.4.2 Second Dword 6-22

6.4.3 Read-Modify-Write Cycles 6-22

6.4.4 Move To/From SFBR Cycles 6-24

6.5 Transfer Control Instructions 6-26

6.5.1 First Dword 6-26

6.5.2 Second Dword 6-33

6.6 Memory Move Instructions 6-33

6.6.1 Read/Write System Memory from SCRIPTS 6-34

6.6.2 Second Dword 6-35

6.6.3 Third Dword 6-35

6.7 Load and Store Instructions 6-37

6.7.1 First Dword 6-38

6.7.2 Second Dword 6-39

Chapter 7 Instruction Set of the I/O Processor

7.1 DC Characteristics 7-1

7.2 TolerANT Technology Electrical Characteristics 7-7

7.3 AC Characteristics 7-10

7.4 PCI and External Memory Interface Timing Diagrams 7-13

7.4.1 Target Timing 7-15

7.4.2 Initiator Timing 7-24

7.4.3 External Memory Timing 7-32

7.5 PCI and External Memory Interface Timing 7-50

7.6 SCSI Timing Diagrams 7-51

7.7 Package Drawings 7-58

Appendix A Register Summary

Appendix B External Memory Interface Diagram Examples

x Contents

Index

Customer Feedback

Figures

1.1 LSI53C875 External Memory Interface 1-2

1.2 LSI53C875 Chip Block Diagram 1-3

2.1 DMA FIFO Sections 2-15

2.2 LSI53C875 Host Interface Data Paths 2-16

2.3 Differential Wiring Diagram 2-22

2.4 Regulated Termination 2-24

2.5 Determining the Synchronous Transfer Rate 2-26

2.6 Block Move and Chained Block Move Instructions 2-35

4.1 LSI53C875 Pin Diagram 4-2

4.2 LSI53C875J Pin Diagram 4-3

4.3 LSI53C875N Pin Diagram 4-4

4.4 LSI53C875JB Pin Diagram (Top View) 4-5

4.5 LSI53C875 Functional Signal Grouping 4-9

6.1 SCRIPTS Overview 6-4

6.2 Block Move Instruction Register 6-7

6.3 I/O Instruction Register 6-15

6.4 Read/Write Instruction Register 6-23

6.5 Transfer Control Instructions 6-28

6.6 Memory Move Instruction 6-36

6.7 Load and Store Instruction Format 6-40

7.1 Rise and Fall Time Test Conditions 7-8

7.2 SCSI Input Filtering 7-8

7.3 Hysteresis of SCSI Receiver 7-9

7.4 Input Current as a Function of Input Voltage 7-9

7.5 Output Current as Function of Output Voltage 7-10

7.6 Clock Waveforms 7-11

7.7 Reset Input 7-12

7.8 Interrupt Output 7-13

7.9 PCI Configuration Register Read 7-15

7.10 PCI Configuration Register Write 7-16

7.11 Operating Register/SCRIPTS RAM Read 7-17

Contents xi

7.12 Operating Register/SCRIPTS RAM Write 7-18

7.13 External Memory Read 7-20

7.14 External Memory Write 7-22

7.15 Opcode Fetch, Nonburst 7-24

7.16 Burst Opcode Fetch 7-25

7.17 Back-to-Back Read 7-26

7.18 Back-to-Back Write 7-27

7.19 Burst Read 7-28

7.20 Burst Write 7-30

7.21 Read Cycle, Normal/Fast Memory ( 64 Kbytes),

Single Byte Access 7-32

7.22 Write Cycle, Normal/Fast Memory ( 64 Kbytes),

Single Byte Access 7-34

7.23 Read Cycle, Normal/Fast Memory ( 64 Kbyte),

Multiple Byte Access 7-36

7.24 Write Cycle, Normal/Fast Memory ( 64 Kbyte),

Multiple Byte Access 7-38

7.25 Read Cycle, Slow Memory ( 64 Kbyte) 7-40

7.26 Write Cycle, Slow Memory ( 64 Kbyte) 7-42

7.27 Read Cycle, Normal/Fast Memory ( 64 Kbyte) 7-44

7.28 Write Cycle, Normal/Fast Memory ( 64 Kbyte) 7-45

7.29 Read Cycle, Slow Memory (£ 64 Kbyte) 7-46

7.30 Write Cycle, Slow Memory (£ 64 Kbyte) 7-48

7.31 Initiator Asynchronous Send 7-51

7.32 Initiator Asynchronous Receive 7-52

7.33 Target Asynchronous Send 7-52

7.34 Target Asynchronous Receive 7-53

7.35 Initiator and Target Synchronous Transfer 7-53

7.36 169-Pin PBGA (GV) Mechanical Drawing 7-58

7.37 160-pin PQFP (P3) Mechanical Drawing 7-59

B.1 64 Kbyte Interface with 200 ns Memory B-1

B.2 64 Kbyte Interface with 150 ns Memory B-2

B.3 256 Kbyte Interface with 150 ns Memory B-3

B.4 512 Kbyte Interface with 150 ns Memory B-4

xii Contents

Tables

2.1 External Memory Support 2-7

2.2 Bits Used for Parity Control and Generation 2-13

2.3 SCSI Parity Control 2-14

2.4 SCSI Parity Errors and Interrupts 2-15

2.5 Differential Mode 2-20

3.1 PCI Bus Commands and Encoding Types 3-3

3.2 PCI Configuration Register Map 3-12

4.1 LSI53C875, LSI53C875J, LSI53C875E, and LSI53C875JE

Power and Ground Signals 4-7

4.2 LSI53C875N Power and Ground Signals 4-7

4.3 LSI53C875JB and LSI53C875JBE Power and

Ground Signals 4-8

4.4 System Signals 4-10

4.5 Address and Data Signals 4-11

4.6 Interface Control Signals 4-12

4.7 Arbitration Signals 4-13

4.8 Error Reporting Signals 4-14

4.9 SCSI SIgnals 4-15

4.10 Additional Interface Signals 4-18

4.11 External Memory Interface Signals 4-21

4.12 JTAG Signals (LSI53C875J/LSI53C875N/LSI53C875JB

Only) 4-22

4.13 Subsystem Data Configuration Table for the LSI53C875E

(PCI Rev ID 0x26) 4-23

4.14 Subsystem Data Configuration Table for the LSI53C875

(PCI Rev ID 0x04), Revision G Only 4-23

4.15 External Memory Support 4-24

5.1 LSI53C875 Register Map 5-2

5.2 Examples of Synchronous Transfer Periods for SCSI-1

Transfer Rates 5-16

5.3 Example Transfer Periods for Fast SCSI-2 and Ultra SCSI

Transfer Rates 5-17

5.4 Maximum Synchronous Offset 5-18

5.5 SCSI Synchronous Data FIFO Word Count 5-28

6.1 SCRIPTS Instructions 6-2

6.2 Read/Write Instructions 6-24

Contents xiii

7.1 Absolute Maximum Stress Ratings 7-2

7.2 Operating Conditions 7-2

7.3 SCSI Signals—SD[15:0]/, SDP[1:0]/, SREQ/, SACK/ 7-3

7.4 SCSI Signals—SMSG, SI_O/, SC_D/, SATN/, SBSY/,

SSEL/, SRST/ 7-3

7.5 Input Signals—CLK, SCLK, GNT/, IDSEL, RST/,

TESTIN, DIFFSENS, BIG_LIT/ 7-3

7.6 Capacitance 7-4

7.7 Output Signals—MAC/_TESTOUT, REQ/ 7-4

7.8 Output Signals—IRQ/, SDIR[15:0], SDIRP0, SDIRP1,

BSYDIR, SELDIR, RSTDIR, TGS, IGS, MAS/[1:0], MCE/,

MOE/, MWE/ 7-4

7.9 Output Signal—SERR/ 7-4

7.10 Bidirectional Signals—AD[31:0], C_BE[3:0], FRAME/,

IRDY/, TRDY/, DEVSEL/, STOP/, PERR/, PAR 7-5

7.11 Bidirectional Signals—GPIO0_FETCH/, GPIO1_MASTER/,

GPIO2_MAS2/, GPIO3, GPIO4 7-5

7.12 Bidirectional Signals—MAD[7:0] 7-6

7.13 Input Signals—TDI, TMS, TCK (LSI53C875J,

LSI53C875JB, LSI53C875N Only) 7-6

7.14 Output Signal—TDO (LSI53C875, LSI53C875JB,

LSI53C875N Only) 7-6

7.15 TolerANT Technology Electrical Characteristics 7-7

7.16 Clock Timing 7-11

7.17 Reset Input 7-12

7.18 Interrupt Output 7-13

7.19 LSI53C875 PCI and External Memory Interface Timing 7-50

7.20 Initiator Asynchronous Send 7-51

7.21 Initiator Asynchronous Receive 7-52

7.22 Target Asynchronous Send 7-52

7.23 Target Asynchronous Receive 7-53

7.24 SCSI-1 Transfers (SE, 5.0 Mbytes/s) 7-54

7.25 SCSI-1 Transfers (Differential, 4.17 Mbytes/s) 7-54

7.26 SCSI-2 Fast Transfers 10.0 Mbytes/s (8-Bit Transfers)

or 20.0 Mbytes/s (16-Bit Transfers), 40 MHz Clock 7-55

7.27 SCSI-2 Fast Transfers 10.0 Mbytes/s (8-Bit Transfers)

or 20.0 Mbytes/s (16-Bit Transfers), 50 MHz Clock 7-55

7.28 Ultra SCSI SE Transfers 20.0 Mbytes/s (8-Bit Transfers)

or 40.0 Mbytes/s (16-Bit Transfers), 80 MHz Clock 7-56

LSI53C875/875E PCI to Ultra SCSI I/O Processor 1-1

Chapter 1

General Description

Chapter 1 is divided into the following sections:

• Section 1.1, “Package and Feature Options”

• Section 1.2, “Benefits of Ultra SCSI”

• Section 1.3, “TolerANT

®

Technology”

• Section 1.4, “LSI53C875 Benefits Summary”

This manual combines information on the LSI53C875 and LSI53C875E,

which are PCI to Ultra SCSI I/O Processors. The LSI53C875E is a minor

modification of the existing LSI53C875 product. It has all the functionality

of the LSI53C875 with the addition of features to enable it to comply with

the Microsoft PC 97 Hardware Design Guide. Specifically, the

LSI53C875E has a Power Management Support enhancement. Because

there are only slight differences between them, the LSI53C875 and

LSI53C875E are referred to as LSI53C875 throughout this technical

manual. Only the new enhancements are referred to as LSI53C875E.

This technical manual assumes the user is familiar with the current and

proposed standards for SCSI and PCI. For additional background

information on these topics, please refer to the list of reference materials

provided in the Preface of this document.

The LSI53C875 brings high-performance I/O solutions to host adapter,

workstation, and general computer designs, making it easy to add SCSI

to any PCI system. The LSI53C875 has a local memory bus for local

storage of the device’s BIOS ROM in Flash memory or standard

EPROMs. Most versions of the LSI53C875 support big and little endian

byte addressing to accommodate a variety of data configurations. The

LSI53C875 supports programming of local Flash memory for updates to

BIOS or SCRIPTS™ programs.

1-2 General Description

The LSI53C875 is a pin-for-pin replacement for the LSI53C825 PCI to

SCSI I/O processor, with added support for the SCSI-3 Ultra standard as

well as other new features. Some software enhancements are needed to

take advantage of the features and Ultra SCSI transfer rates supported

by the LSI53C875. The LSI53C875 performs Ultra SCSI transfers or fast

8- or 16- bit SCSI transfers in Single-Ended (SE) or differential mode,

and improves performance by optimizing PCI bus utilization. A system

diagram showing the connections of the LSI53C875 with an external

ROM or Flash memory is pictured in Figure 1.1.

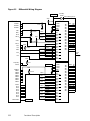

Figure 1.1 LSI53C875 External Memory Interface

PCI Bus

SCSI Bus

BIG_LIT

LSI53C875

GPIO2_MAS2/

MAS1/

MWE/

MOE/

MCE/

MAD[7:0]

MAS0/

GPIO4

V

PP

Translator

V

PP

(Optional)

V

PP

HCT374

HCT374

HCT374

ROM or Flash

D[7:0]

A[7:0]

A[15:8]

A[19:16]

(Optional)

Memory

1-3

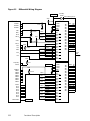

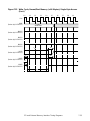

A block diagram of the LSI53C875 is pictured in Figure 1.2.

Figure 1.2 LSI53C875 Chip Block Diagram

The LSI53C875 integrates a high-performance SCSI core, a PCI bus

master DMA core, and the LSI Logic SCSI SCRIPTS processor to meet

the flexibility requirements of SCSI-3 and Ultra SCSI standards. It is

designed to implement multithreaded I/O algorithms with a minimum of

processor intervention, solving the protocol overhead problems of

previous intelligent and nonintelligent adapter designs.

The LSI53C875 is fully supported by the LSI Logic Storage Device

Management System (SDMS™), a software package that supports the

Advanced SCSI Protocol Interface (ASPI) and the ANSI Common

Access Method (CAM). SDMS software provides BIOS and driver

support for hard disk, tape, removable media products, and CD-ROM

under the major PC operating systems.

PCI Master and Slave Control Block

Data

FIFO

536 Bytes

Memory

Control

SCSI

SCRIPTS

Processor

Operating

Registers

Configuration

Registers

SCRIPTS

RAM

SCSI FIFO and SCSI Control Block

Local

Bus

Memory

TolerANT Drivers and Receivers

SCSI Bus

External

Memory

PCI

1-4 General Description

1.1 Package and Feature Options

The LSI53C875 is available in three versions with different packaging

and feature options. The LSI53C875 is packaged in a 160-pin Plastic

Quad Flat Pack (PQFP). The LSI53C875J is identical to the LSI53C875

with additional pins that support JTAG boundary scan testing. The JTAG

boundary scan signals replace the TESTIN, MAC/_TESTOUT, BIG_LIT/,

and SDIRP1 pins.

The LSI53C875N includes all of the signals in the LSI53C875, with the

addition of the JTAG pins and four additional signals for extended parity

checking and generation. It is packaged in a 208-pin PQFP.

The LSI53C875JB is identical to the LSI53C875J, but is packaged in a

169-pin Ball Grid Array (BGA). The LSI53C875E, LSI53C875JE, and

LSI53C875JBE have been upgraded to include the power management

features.

1.2 Benefits of Ultra SCSI

Ultra SCSI is an extension of the SCSI-3 standard that expands the

bandwidth of the SCSI bus and allows faster synchronous SCSI transfer

rates. When enabled, Ultra SCSI performs 20 megatransfers during an

I/O operation, resulting in approximately twice the synchronous transfer

rates of fast SCSI-2. The LSI53C875 can perform 8-bit, Ultra SCSI

synchronous transfers as fast as 20 Mbytes/s. This advantage is most

noticeable in heavily loaded systems, or large block size requirements,

such as video on-demand and image processing.

An advantage of Ultra SCSI is that it significantly improves SCSI

bandwidth while preserving existing hardware and software investments.

The LSI53C875 is compatible with all existing LSI53C825 and

LSI53C825A software; the only changes required are to enable the chip

to perform synchronous negotiations for Ultra SCSI rates. The

LSI53C875 can use the same board socket as an LSI53C825, with the

addition of an 80 MHz SCLK or enabling the internal SCSI clock doubler

to provide the correct frequency when transferring synchronous SCSI

data at 50 nanosecond transfer rates. Some changes to existing cabling

or system designs may be needed to maintain signal integrity at Ultra

SCSI synchronous transfer rates. These design issues are discussed in

Chapter 2, “Functional Description.”

TolerANT

®

Technology 1-5

1.3 TolerANT

®

Technology

The LSI53C875 features TolerANT technology, which includes active

negation on the SCSI drivers and input signal filtering on the SCSI

receivers. Active negation actively drives the SCSI Request,

Acknowledge, Data, and Parity signals HIGH rather than allowing them

to be passively pulled up by terminators. Active negation is enabled by

setting bit 7 in the SCSI Test Three (STEST3) register.

TolerANT receiver technology improves data integrity in unreliable

cabling environments, where other devices would be subject to data

corruption. TolerANT receivers filter the SCSI bus signals to eliminate

unwanted transitions, without the long signal delay associated with

RC-type input filters. This improved driver and receiver technology helps

eliminate double clocking of data, the single biggest reliability issue with

SCSI operations. TolerANT technology input signal filtering is a built-in

feature of the LSI53C875 and all LSI Logic fast SCSI devices. On the

LSI53C875, the user may select a filtering period of 30 or 60 ns, with

bit 1 in the SCSI Test Two (STEST2) register.

The benefits of TolerANT technology include increased immunity to noise

when the signal is going HIGH, better performance due to balanced duty

cycles, and improved fast SCSI transfer rates. In addition, TolerANT

SCSI devices do not cause glitches on the SCSI bus at power-up or

power-down, so other devices on the bus are also protected from data

corruption. TolerANT technology is compatible with both the Alternative

One and Alternative Two termination schemes proposed by the

American National Standards Institute.

1-6 General Description

1.4 LSI53C875 Benefits Summary

The section provides an overview of the LSI53C875 features and

benefits. It contains information on SCSI Performance, PCI Performance,

Integration, Ease of Use, Flexibility, Reliability, and Testability.

1.4.1 SCSI Performance

To improve SCSI performance, the LSI53C875:

• Includes 4 Kbyte internal RAM for SCRIPTS instruction storage.

• Performs wide, Ultra SCSI synchronous transfers as fast as

40 Mbytes/s.

• Increases SCSI synchronous offset from 8 to 16 levels.

• Supports variable block size and scatter/gather data transfers.

• Performs sustained memory-to-memory DMA transfers faster than

47 Mbytes/s (@ 33 MHz).

• Minimizes SCSI I/O start latency.

• Performs complex bus sequences without interrupts, including

restore data pointers.

• Reduces interrupt service routine overhead through a unique

interrupt status reporting method.

• Performs fast and wide SCSI bus transfers in SE and differential

mode.

– 10 Mbytes/s asynchronous (20 Mbytes/s with Ultra SCSI).

– 20 Mbytes/s synchronous (40 Mbytes/s with Ultra SCSI).

• Supports Load and Store SCRIPTS instructions to increase the

performance of data transfers to and from chip registers.

• Supports target disconnect and later reconnect with no interrupt to

the system processor.

• Supports multithreaded I/O algorithms in SCSI SCRIPTS with fast

I/O context switching.

• Supports expanded Register Move instructions to support additional

arithmetic capability.

• Complies with PCI Bus Power Management Specification

(LSI53C875E) Revision 1.0.

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

-

1

1

-

2

2

-

3

3

-

4

4

-

5

5

-

6

6

-

7

7

-

8

8

-

9

9

-

10

10

-

11

11

-

12

12

-

13

13

-

14

14

-

15

15

-

16

16

-

17

17

-

18

18

-

19

19

-

20

20

-

21

21

-

22

22

-

23

23

-

24

24

-

25

25

-

26

26

-

27

27

-

28

28

-

29

29

-

30

30

-

31

31

-

32

32

-

33

33

-

34

34

-

35

35

-

36

36

-

37

37

-

38

38

-

39

39

-

40

40

-

41

41

-

42

42

-

43

43

-

44

44

-

45

45

-

46

46

-

47

47

-

48

48

-

49

49

-

50

50

-

51

51

-

52

52

-

53

53

-

54

54

-

55

55

-

56

56

-

57

57

-

58

58

-

59

59

-

60

60

-

61

61

-

62

62

-

63

63

-

64

64

-

65

65

-

66

66

-

67

67

-

68

68

-

69

69

-

70

70

-

71

71

-

72

72

-

73

73

-

74

74

-

75

75

-

76

76

-

77

77

-

78

78

-

79

79

-

80

80

-

81

81

-

82

82

-

83

83

-

84

84

-

85

85

-

86

86

-

87

87

-

88

88

-

89

89

-

90

90

-

91

91

-

92

92

-

93

93

-

94

94

-

95

95

-

96

96

-

97

97

-

98

98

-

99

99

-

100

100

-

101

101

-

102

102

-

103

103

-

104

104

-

105

105

-

106

106

-

107

107

-

108

108

-

109

109

-

110

110

-

111

111

-

112

112

-

113

113

-

114

114

-

115

115

-

116

116

-

117

117

-

118

118

-

119

119

-

120

120

-

121

121

-

122

122

-

123

123

-

124

124

-

125

125

-

126

126

-

127

127

-

128

128

-

129

129

-

130

130

-

131

131

-

132

132

-

133

133

-

134

134

-

135

135

-

136

136

-

137

137

-

138

138

-

139

139

-

140

140

-

141

141

-

142

142

-

143

143

-

144

144

-

145

145

-

146

146

-

147

147

-

148

148

-

149

149

-

150

150

-

151

151

-

152

152

-

153

153

-

154

154

-

155

155

-

156

156

-

157

157

-

158

158

-

159

159

-

160

160

-

161

161

-

162

162

-

163

163

-

164

164

-

165

165

-

166

166

-

167

167

-

168

168

-

169

169

-

170

170

-

171

171

-

172

172

-

173

173

-

174

174

-

175

175

-

176

176

-

177

177

-

178

178

-

179

179

-

180

180

-

181

181

-

182

182

-

183

183

-

184

184

-

185

185

-

186

186

-

187

187

-

188

188

-

189

189

-

190

190

-

191

191

-

192

192

-

193

193

-

194

194

-

195

195

-

196

196

-

197

197

-

198

198

-

199

199

-

200

200

-

201

201

-

202

202

-

203

203

-

204

204

-

205

205

-

206

206

-

207

207

-

208

208

-

209

209

-

210

210

-

211

211

-

212

212

-

213

213

-

214

214

-

215

215

-

216

216

-

217

217

-

218

218

-

219

219

-

220

220

-

221

221

-

222

222

-

223

223

-

224

224

-

225

225

-

226

226

-

227

227

-

228

228

-

229

229

-

230

230

-

231

231

-

232

232

-

233

233

-

234

234

-

235

235

-

236

236

-

237

237

-

238

238

-

239

239

-

240

240

-

241

241

-

242

242

-

243

243

-

244

244

-

245

245

-

246

246

-

247

247

-

248

248

-

249

249

-

250

250

-

251

251

-

252

252

-

253

253

-

254

254

-

255

255

-

256

256

-

257

257

-

258

258

-

259

259

-

260

260

-

261

261

-

262

262

-

263

263

-

264

264

-

265

265

-

266

266

-

267

267

-

268

268

-

269

269

-

270

270

-

271

271

-

272

272

-

273

273

-

274

274

-

275

275

-

276

276

-

277

277

-

278

278

-

279

279

-

280

280

-

281

281

-

282

282

-

283

283

-

284

284

-

285

285

-

286

286

-

287

287

-

288

288

-

289

289

-

290

290

-

291

291

-

292

292

-

293

293

-

294

294

-

295

295

-

296

296

-

297

297

-

298

298

-

299

299

-

300

300

-

301

301

-

302

302

-

303

303

-

304

304

-

305

305

-

306

306

-

307

307

-

308

308

-

309

309

-

310

310

-

311

311

-

312

312

-

313

313

-

314

314

Broadcom LSI53C875-875E PCI to Ultra SCSI I-O Processor technical User guide

- Type

- User guide

- This manual is also suitable for

Ask a question and I''ll find the answer in the document

Finding information in a document is now easier with AI

Related papers

-

LSI LSI53C140 Ultra2 SCSI bus expander product brief User guide

-

LSI SEN S11005 - Requirements for Synchronous Negotiation When Using the SYM53C140 in System User manual

-

LSI LSIU40SE Dual Channel PCI to Ultra SCSI Host Adapter User guide

-

Broadcom LSI53C1020 Ultra320 SCSI User guide

-

LSI I-O Controller Selector Product Brief User guide

-

Broadcom LSIMPT_SCSI_WinXP User guide

-

LSI LSIMPT_SCSI_W2k3 User guide

-

LSI LSI53C1030 Ultra320 SCSI product brief User guide

-

Broadcom LSI53C120 HVD SCSI product brief User guide

-

Broadcom README_FOR_nw1010_50308 User guide

Other documents

-

LogiLink PC0018 Datasheet

-

LSI LSI8750SP PCI to Ultra SCSI Host Adapter User guide

-

LSI 8751D User manual

-

LSI LSI53C120 Ultra SCSI Bus Expander User guide

-

Rega Ania Mounting Guide

-

LSI 53C875A User manual

-

LSI LSI22903 PCI to Dual Channel Ultra 160 SCSI Low Profile Host Adapter User guide

-

LSI U80ALVD User manual

-

Lexicon MPX - ADDENDUM REV 1 Technical Manual

-

LSI LSI21003 PCI to Dual Channel SCSI Host Adapter User manual