Page is loading ...

AN10050

Designing a Hi-Speed USB host PCI adapter using the

ISP1562, ISP1563

Rev. 04 — 1 November 2007 Application note

Document information

Info Content

Keywords isp1562; isp1563; usb; universal serial bus; host; pci adapter

Abstract This document contains a description of the ISP1562/3 application

schematics and the PCB design recommendations.

NXP Semiconductors

AN10050

Designing a Hi-Speed USB host PCI adapter using ISP1562/63

AN10050_4 © NXP B.V. 2007. All rights reserved.

Application note Rev. 04 — 1 November 2007 2 of 18

Contact information

For additional information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: [email protected]

Revision history

Rev Date Description

04 20071101 Fourth revision. Corrected typo in Section 4: it is 2.5 inches ± 0.1 inch, not ± 1 inch.

Last line of Section

3.4.

03 20061212 Third revision. Updated Fig 6.

02 20060707 Second revision. Updated Section 5.

01 20051004 First release.

NXP Semiconductors

AN10050

Designing a Hi-Speed USB host PCI adapter using ISP1562/63

AN10050_4 © NXP B.V. 2007. All rights reserved.

Application note Rev. 04 — 1 November 2007 3 of 18

1. Introduction

The ISP1562 and the ISP1563 are Hi-Speed Universal Serial Bus (USB) host controllers

(HCs) that can be directly connected to a standard 32-bit, 33 MHz PCI bus. For the rest

of this document, they will be known as ‘ISP1562/3’. The ISP1562/3 complies with PCI

Local Bus Specification Rev. 2.2 and PCI Bus Power Management Interface

Specification Rev. 1.1. No additional logic is required to implement a complete Hi-Speed

USB host controller solution on Peripheral Component Interconnect (PCI).

Adapter cards based on the ISP1562/3 implement three functions: function 0 and

function 1 for OHCI1 and OHCI2, and function 2 for EHCI. According to PCI Local Bus

Specification, each physical PCI device may incorporate one to eight separate functions

(logical devices). Each function contains its own memory-mapped individually

addressable configuration space of 256 bytes, containing configuration registers.

The configuration registers of the ISP1562/3 are used by the system’s BIOS and the

operating system to detect the presence of the respective functions, that is, Vendor ID

(VID) and Product ID (PID), to determine the necessary resource requirements, that is,

memory and I/O space, interrupt lines, and so on, and for specific capabilities.

A set of on-chip ‘operational’ registers is also defined for each of the three host

controllers implemented in the ISP1562/3. The respective host controller device driver

interacts with these registers to implement the USB functionality and the legacy support.

A detailed description of configuration registers and operational registers can be found in

the ISP1562 and ISP1563 data sheets.

The ISP1562/3 implements two internal ‘power wells’, V

DD

and V

DDX

, to benefit from the

PCI V

AUX

= 3.3 V dedicated power source, which is present on the PCI connector (pin

A14) even when PCI V

CC

= 3.3 V is off. This enables the ISP1562/3 PME# signal to be

asserted and activates the wake-up logic of the motherboard, even if the rest of the

system is powered down; for example, in S3

cold

system standby mode. This is applicable

mainly to onboard (desktop) or mobile designs, but not applicable to PCI add-on cards

because the PCI +5 V, used for V

BUS

, is also off during S3

cold

.

The ISP1562/3 may use PCI V

AUX

to power its four internal transceivers connected to the

ISP1562/3 V

DDA_AUX

(analog), and also the clock circuitry, port router, root hub and Power

Management Event (PME#) logic connected to the ISP1562/3

V

CC(I/O)_AUX

(digital).

For details on implementation of the PCB design, see Section

4.

The power management capabilities enabled by using PCI V

AUX

allow system designers

to meet the governmental energy regulations that are becoming increasingly essential

worldwide: Energy Star/USA: 30 W standby, White Swan/Europe: 5 W standby, Blue

Angel/Europe: 5 W standby.

This document provides a description of the application schematics and the PCB design

recommendations.

2. ISP1562/3 initialization

The following sequence is required during the ISP1562/3 initialization, for correct

functionality:

1. Register HcRhDescriptorA = 902h. This means that bit PSM = 1b.

2. Register HcControl = 680h. This means that bits HCFS[1:0] = 10b (operational

mode).

NXP Semiconductors

AN10050

Designing a Hi-Speed USB host PCI adapter using ISP1562/63

AN10050_4 © NXP B.V. 2007. All rights reserved.

Application note Rev. 04 — 1 November 2007 4 of 18

3. Register HcRhStatus = 18000h. This implies that bit LPSC = 1b (port powered).

Microsoft Windows 2000, Windows XP and Linux drivers normally use this sequence.

The order of the steps may, however, be reversed in Windows CE default drivers so

changes are required for normal functionality.

3. Description of the application schematics

The schematics (see Section 5) contain a complete implementation of the ISP1562/3 and

allow testing of all its features in different types of design: PCI add-on card, onboard

design in standard desktop or mobile solution.

In the case of a standard PCI add-on card design, some simplifications to the schematics

can be done, as described here. Some features will not be normally used in a standard

PCI add-on card. For example: The legacy support, wake-up from S3

cold

(no external

+5 V input for V

BUS

) and the alternative 48 MHz clock input. All these alternatives,

however, are included in the schematics and are described in this document.

3.1 Distribution of power sources and power management support

As shown in the schematics (see Section 5), a simple solution by using one jumper (JP1)

may be adopted to choose between PCI V

CC

= 3.3 V or PCI V

AUX

= 3.3 V as the main

power source for the ISP1562/3. Power source PCI V

AUX

= 3.3 V is introduced in PCI

Local Bus Specification Revision 2.2. It allows powering an add-on card and generation

of the PME# signal, even if the system is in a deep power management state and PCI

V

CC

is off. An alternative solution to using a jumper may be a simple circuit containing a

pair of MOSFET transistors that allows to detect the presence of PCI V

AUX

= 3.3 V and

automatic selection of the input voltage.

Selection of PCI V

CC

= +3.3 V must be the default position of jumper JP1 in the case of a

standard add-on card design. The other possible position of JP1 selects PCI V

AUX

= 3.3 V

for complete Power Management tests, including S3

cold

in the case of on-motherboard or

notebook. Note that pins 3, 77, 98 and 100 of the ISP1562, and pins 6, 12 and 95 of the

ISP1563 are connected to the PCB V

CC(I/O)_AUX

power plane and pins 86 and 93 of the

ISP1562, and pins 104, 111, 120 and 128 of the ISP1563 are connected to the PCB

V

DDA_AUX

power plane. Each of these planes is separated from PCI V

AUX

by its own set of

inductors and decoupling capacitors.

Although most of the motherboards provide the PCI V

AUX

power source in all system

power management modes, including S3

cold

, the PCI +5 V power supply is

simultaneously interrupted with PCI V

CC

= +3.3 V.

In certain standby modes (S3

cold

), the devices connected to USB ports will not be

powered once the +5 V power is removed because the V

BUS

voltage present on USB

connectors is normally derived from the PCI +5 V power supply. Therefore, PCI V

AUX

is

not useful in the case of a standard PCI add-on card implementation for a system wake-

up from S3

cold

. It is, however, a very useful feature for onboard and mobile application

designs because it allows additional considerable power savings and also wakes up the

system by using a USB device. The system wake-up from S3

cold

, generated from a USB

device, for example, USB mouse or USB keyboard, connected to the ISP1562/3 host

controller must be supported in system’s BIOS, hardware (a continuous +5 V must be

supplied to V

BUS

) and operating system drivers.

To be able to test the remote wake-up, especially, from those power management states

in which the +5 V power source on PCI is not present, for example, S3

cold

, a special

connector (J1) is added for an external +5 V source. Any external independent power

NXP Semiconductors

AN10050

Designing a Hi-Speed USB host PCI adapter using ISP1562/63

AN10050_4 © NXP B.V. 2007. All rights reserved.

Application note Rev. 04 — 1 November 2007 5 of 18

supply that provides +5 V ± 5 % @ 2 A stabilized can be used. For example, a standard

hub power supply.

Note the distribution of pull-up resistors in the recommended schematics. For example,

to achieve correct functionality, it is recommended that you connect the pull-up resistors

placed on the PWEn_N and OCn_N input signals of the power switch, for example,

MIC2026, to DV

AUX

NET, maintaining a good condition of these signals even when

+3.3 V and +5 V are off. The ‘fault flag’ pins (OCn_N) of MIC2026 are open-drain and

require the presence of pull-up resistors. A 100 nF capacitor is used on each OCn_N

signal to prevent false fault conditions.

CLKRUN# is implemented in the ISP1562 on pin 42 and in the ISP1563 on pin 52. This

signal is targeted mainly for mobile system designs. CLKRUN is an I/O pin. It is used by

the system to safely turn-off the PCI CLK for power saving, with acknowledgment from

the ISP1562/3 according to a predefined protocol. In the case of the PCI adapter card

design, CLKRUN# must always be LOW because it is not present in the PCI connector.

CLKRUN# may directly be connected to GND. For details on CLKRUN# function, refer to

PCI Mobile Design Guide Version 1.1.

3.2 Input clock: applies only to the ISP1563

You can use either of the following as clock input:

• A 12 MHz crystal; the default recommended solution for best ElectroMagnetic

Interference (EMI) results.

• A 48 MHz oscillator; this may be a useful alternative, typically, in the case of on-

motherboard design.

Both solutions for the input clock are shown in the schematics.

To use a 48 MHz clock as input, connect the clock signal to the ISP1563 pin 86 (XTAL1),

pin 87 (XTAL2) can be left open, and pin 121 (SEL48M) must be pulled up as shown in

the schematics.

In an add-on card configuration, normally, the 12 MHz crystal is used. In such a case,

oscillators OSC2 and R45 are not necessary. Also, pin 121 (SEL48M) must directly be

connected to GND. Another possibility is using a 12 MHz clock as an input. In this case,

the 12 MHz-clock signal is directly connected to the ISP1563 pin 86 (XTAL1). This is

similar to the case in which the 48 MHz clock is used; however, the ISP1563 pin 121

must still be connected to GND.

3.3 Selecting the number of ports: applies only to the ISP1563

The selection of the number of ports, 2 or 4, is done using the SEL2PORTS signal

(ISP1563 pin 5). It must be pulled to LOW, that is, connected to GND, for normal use of

all four ports. If SEL2PORTS is HIGH, only two ports, that is, port 1 and port 2, are

enabled; one port from each OHCI will be used in this case for performance

improvement. Details regarding the power consumption and possible power savings in a

two-port configuration can be found in the ISP1563 data sheet.

3.4 Subsystem vendor ID and subsystem device ID

The ISP1562/3 allows loading of the Subsystem Vendor ID (VID) and the Subsystem

Device ID (DID) for both EHCI and OHCI from an external EEPROM. Loading of these

values in the configuration registers of the ISP1562/3 will occur only if a value of 15h is

found in byte 7 of the EEPROM. The necessary signals, I

2

C-bus clock and I

2

C-bus data,

NXP Semiconductors

AN10050

Designing a Hi-Speed USB host PCI adapter using ISP1562/63

AN10050_4 © NXP B.V. 2007. All rights reserved.

Application note Rev. 04 — 1 November 2007 6 of 18

are defined on pins 96 (SCL) and 97 (SDA) of the ISP1562, and pins 122 (SCL) and 123

(SDA) of the ISP1563, respectively. When not in use, these signals must be connected to

ground using a pull-down resistor, typically 10 kΩ.

3.5 Legacy support: applies only to the ISP1563

Legacy signals, IRQ1, IRQ12, A20OUT, KBIRQ1, MUIRQ12 and SMI#, are not normally

used on a PCI add-on card design. In this case, the MUIRQ12 and KBIRQ1 input signals

must be connected to GND. The other signals that are mentioned in this category (that

are outputs) can be left open.

Details on legacy signals and a block diagram showing correct connection of these

signals in the case of onboard design can be found in ISP1563 Eval Board User Manual

(UM10066).

3.6 Overcurrent protection

The ISP1562/3 implements the digital overcurrent protection scheme.

The recommended solution to implement an external overcurrent protection is a standard

power switch with integrated overcurrent detection, such as:

• LM3526 and MIC2526 (2 ports), or

• LM3544 (4 ports).

The overcurrent protection logic of the ISP1562/3 uses the following two pins for each

USB port:

• PWEn_N: It is used to enable or disable the respective external port power switch.

For example, MIC2526 and LM3526.

• OCn_N: It is an input on which a fault condition on the respective USB port is

signaled to the ISP1562/3 by the external port power-switching device.

The fault condition that is usually signaled by an external power-switching device can be

an overcurrent or a thermal shutdown. The port power-switching integrated devices

commonly implement a delay of 1 ms to 3 ms to prevent false OC_N reporting because

of inrush currents, when plugging a USB device.

Once a fault condition is received, it will be detected by the operating system and the

respective device driver will disable the port power switch by programming the Port

Power (PP) bit in the PORTSC register. This device driver is the OHCI driver in the case

of an Original USB device to create the fault condition, or the EHCI driver in the case of a

Hi-Speed USB device to create the overcurrent condition. This is according to the USB

port allocation at the moment when the OC# signal was asserted.

A possible alternative is to use a resettable fuse on each port. This has the advantage of

simplicity. It, however, does not inform the operating system of the fault condition and,

therefore, no message is generated to inform the user. The resettable fuse will continue

to protect the port by switching ‘on or off’ as long as the overcurrent condition persists.

A possible enhancement of this scheme is connecting V

BUS

to the OCn_N input of the

ISP1562/3 to detect the OCn_N condition, the first time V

BUS

is cut-off a LOW level will

appear on the OCn_N pin.

Using only an external PMOS transistor for overcurrent protection is not possible

because the ISP1562/3 does not implement the analog overcurrent protection (not

measuring the current through the transistor).

NXP Semiconductors

AN10050

Designing a Hi-Speed USB host PCI adapter using ISP1562/63

AN10050_4 © NXP B.V. 2007. All rights reserved.

Application note Rev. 04 — 1 November 2007 7 of 18

4. PCB design recommendations

Some important recommendations for a successful PCB design, applicable to both

adapter card and motherboard design solutions, are as follows:

• Typically, a solution using four layers PCB (signal 1, GND, V

CC

, signal 2) is sufficient

for proper routing, allowing you to obtain good functionality and meeting all

compliance tests requirements. Start your design by placing the ISP1562/3 chip, the

major components, and routing of the high-speed DP and DM traces and clock

traces. Also, a complete ‘clean’ solution for routing the power and GND (split planes)

must be defined before you start routing the rest of the signals.

• The trace length for all PCI signals, except the PCI clock signal, to the PCI connector

must be limited to a maximum of 1.5 inches.

• The length of the PCI clock signal from the PCI bus connector to the ISP1562/3 must

be 2.5 inches ± 0.1 inch in length and must be routed to only one load. It must

usually be ‘snaked’. Ensure that all corners of this trace are rounded. Do not use 90°

sharp corners.

• Route the high-speed USB differential pairs over continuous GND or power planes.

Avoid crossing anti-etch areas and any breaks in the internal planes (plane splits).

The minimum recommended distance to a plane split is 25 mils. You must also avoid

placing a series of via holes near the DP and DM lines because these will create

‘break areas’ in the GND plane below. This is because of the clearance imposed by

the manufacturing process around any via holes to an internal plane.

• Try to keep the length of the DP and DM traces equal. The maximum trace length

mismatch between high-speed USB signal pairs must not be greater than 70 mils.

• Maintain parallelism between USB differential signals, with the trace spacing needed

to achieve 90 Ω differential impedance. To achieve the required impedance of the

pair traces, it is recommended that you use 8 mils traces and keep the distance

between the DP and DM traces at 8 mils. These values may vary, depending on the

actual PCB parameters.

• Avoid corners when routing the differential pairs DP and DM. Any 90° direction

change of traces must be accomplished with two 45° turns or by using an arc of an

imaginary circle tangent to the DP and DM lines.

• Avoid routing the USB differential pairs near I/O connectors, signal headers, crystals,

oscillators, magnetic devices and power connectors.

• Maintain the maximum possible distance between high-speed USB differential pairs,

high-speed or low-speed clock, and non-periodic signals. The minimum

recommended distances are as follows:

− 20 mils between the DP and DM traces and low-speed non-periodic signal traces

− 50 mils between the DP and DM traces, and clock or high-speed periodic signal

traces

− 20 mils between two pairs of the DP and DM traces

• Avoid creating stubs to connect the 15 kΩ pull-down resistors or to test points. If a

stub is unavoidable in the design, no stub must be greater than 80 mils.

• Route all the DP and DM lines on one layer. Do not change layers (avoid using vias)

even to avoid crossing a plane split. It is better to place a non-split plane under high-

speed USB signals, ground layer or power layer. It is recommended that you place a

ground layer beneath the DP and DM lines.

NXP Semiconductors

AN10050

Designing a Hi-Speed USB host PCI adapter using ISP1562/63

AN10050_4 © NXP B.V. 2007. All rights reserved.

Application note Rev. 04 — 1 November 2007 8 of 18

• The maximum allowed length of the DP and DM lines for onboard solutions (or [trace

+ cable length] for a front-panel solution) is 18 inches.

• A decoupling capacitor must be placed on V

BUS

as close as possible to each USB

connector. A value of about 150 µF/10 V is recommended on each port.

• The common-mode choke used, if really necessary, on the DP and DM lines must be

placed as close as possible to the USB connector and must have

Z

com

< 8 Ω @ 100 MHz and Z

diff

< 300 Ω @ 100 MHz.

• The common-mode choke, as well as the ElectroStatic Discharge (ESD) protection

components will be used only if necessary (in case the design does not pass EMI or

the ESD tests) because these may affect the signaling quality. Nevertheless, it is

recommended that you include the necessary footprints for common-mode chokes

and ESD protection components on the PCB as safeguards. The footprints must be

placed as close as possible to the USB connector. Special attention must be given

when placing additional components on the DP and DM lines and routing

recommendations must be followed.

• Both V

DDA_AUX

(analog) and V

CC(I/O)_AUX

(digital) are derived from the PCI V

AUX

voltage,

found on pin A14 of the PCI connector.

V

CC(I/O)_AUX

can directly be connected to PCI

V

AUX

. V

DDA_AUX

is separated from PCI V

AUX

by an inductor and each of V

CC(I/O)_AUX

and

V

DDA_AUX

uses its own decoupling capacitors.

• The design must ensure that the V

DDA_AUX

and V

CC(I/O)_AUX

power planes are isolated

from the main PCI 3.3 V power plane. This is achieved by creating two separate

power planes that do not come in contact with the PCI 3.3 V power plane.

• The decoupling capacitors must be placed as close as possible to the ISP1562/3. A

good choice is the four corners of the IC because these areas will not normally be

occupied by traces or other components, according to the ISP1562/3 pinout.

• For good EMI testing results, it is recommended that you provide a good path from

the USB connector shell to the chassis ground. The USB connector shell must be

connected to an isolated ground plane.

For more information, refer to the Intel document The USB 2.0 Platform Design

Guideline, Rev. 1.0.

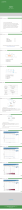

5. Schematics

NXP Semiconductors

AN10050

Designing a Hi-Speed USB host PCI adapter using ISP1562/63

AN10050_4 © NXP B.V. 2007. All rights reserved.

Application note Rev. 04 — 1 November 2007 9 of 18

PCI CONNECTOR

AD[31:0]

PCICLK

RST#

IDSEL

GNT#

C/BE0#

C/BE1#

C/BE2#

C/BE3#

INTA#

REQ#

FRAME#

TRDY#

IRDY#

DEVSEL#

STOP#

PERR#

SERR#

PAR

PME#

AD[31:0]

PCICLK

RST#

IDSEL

GNT#

C/BE0#

C/BE1#

C/BE2#

C/BE3#

INTA#

REQ#

FRAME#

TRDY#

IRDY#

DEVSEL#

STOP#

PERR#

SERR#

PAR

PME#

PWE1#

PWE2#

OC1#

OC2#

DM1

DP1

DM2

DP2

DM1

DP1

DM2

DP2

PWE1#

PWE2#

OC1#

OC2#

ISP1562_ES1

USB PORTS

POWER CONTROL

Fig 1. ISP1562 eval board schematic – top level interfaces

NXP Semiconductors

Designing a Hi-Speed USB host PCI adapter using ISP1562/63

AN10050

Application note

A

N10050

_

4

Rev. 04 — 1 November 2007

10 of 18

© NXP B.V. 2007. All rights reserved.

DV

AUX

C20

0.1 μF

C17

C22

0.1 μF

0.001 μF

+3.3 V

Should be placed

as close as

possible to pin 98

Should be placed

as close as

possible to pin 55

C21

0.1 μF

U2A

A1

A3

GND

VCC

NC/WP

SCL

SDA

AT24C01A-2.7

U2

A0

A1

A3

GND

VCC

NC/WP

SCL

SDA

AT24C01A-2.7

+3.3 V

C9

0.1 μF

R2

0 Ω

R4

R5

R3

0 Ω

R6

0 Ω

1

2

3

4

5

6

7

8

1

2

3

45

6

7

8

Should be placed

as close as

possible to pin 3

C38

0.1 μF

All capacitors should be placed as close as possible

to the corresponding power pins.

AV

AUX

+3.3 V

C49

1 nF

C50

1 nF

C51

1 nF

C31

C32

C33

0.1 μF

0.1 μF

0.1 μF

0.1 μF

C34

C35

C36

C37

0.1 μF

1 nF

1 nF

0.1 μF 0.1 μF

0.1 μF 0.1 μF

0.1 μF

C10

4.7 μF

C23

C24

C25

C26

C27

C30

4.7μF

+

+

+3.3 V

JP1

HEADER 3

3.3 V

AUX

1

2

3 BLM21PG221SN1

C28

C60 C59

0.1 μF

470 pF

47 μF / 6.3 V

AV

AUX

D3 LED

R1

330 Ω

DV

AUX

All capacitors should be placed

as close as possible to the

corresponding ferrite bead

AV

AUX

BLM18PG121SN1

FB2

+

FB 1

C29

C19

0.1 μF

1 nF

C61

+

4.7 μF / 6.3 V

SCL

SDA

96

97

SCL

SDA

AD[0]

AD[1]

AD[2]

AD[3]

AD[4]

AD[5]

AD[6]

AD[7]

AD[8]

AD[9]

AD[10]

AD[11]

AD[12]

AD[13]

AD[14]

AD[15]

AD[16]

AD[17]

AD[18]

AD[19]

AD[20]

AD[21]

AD[22]

AD[23]

AD[24]

AD[25]

AD[26]

AD[27]

AD[28]

AD[29]

AD[30]

AD[31]

AD0

AD1

AD2

AD4

AD3

70

69

68

67

66

65

AD5

AD6

63

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

62

59

57

56

54

53

52

51

50

34

33

31

30

29

28

27

26

22

21

20

15

14

13

12

10

C/BE#[0]

C/BE#[1]

C/BE#[2]

C/BE#[3]

C/BE0#

C/BE1#

C/BE2#

C/BE3#

60

48

35

23

78

87

OC1#

OC2#

PWE1#

PWE2#

DM1

DM2

DP1

DP2

79

88

83

90

85

92

OC1_N

OC2_N

PWE1_N

PWE2_N

DM1

DM2

DP1

DP2

RREF

GNDA

XTAL1

XTAL2

81

80

74

75

R7

12 kΩ / 1 %

C62

C63

OSC1

12 MHz

OC1#

OC2#

PWE1#

PWE2#

DM1

DM2

DP1

DP2

PME#

PCICLK

RST#

PA R

SERR#

PERR#

CLKRUN#

STOP#

DEVSEL#

TRDY#

IRDY#

FRAME#

IDSEL

GNT#

REQ#

INTA#

PME#

PCICLK

RST#

PA R

SERR#

PERR#

STOP#

DEVSEL#

TRDY#

IRDY#

FRAME#

IDSEL

GNT#

REQ#

INTA#

PME#

PCICLK

RST#

PA R

SERR#

PERR#

STOP#

DEVSEL#

TRDY#

IRDY#

FRAME#

IDSEL

GNT#

REQ#

INTA#

99

7

5

47

45

44

42

41

39

38

37

36

24

8

9

4

C/BE0#

C/BE1#

C/BE2#

C/BE3#

U1

ISP1562ESP

AUX1V18

AUX1V18

REG1V18

REG1V18

REG1V18

V

I(VREG3V3)

V

CC(I/O)

V

CC(I/O

)

V

CC(I/O)

V

CC(I/O)

V

CC(I/O)

V

I(VAUX3V3)

V

CC(I/O)_AUX

V

CC(I/O)_AUX

V

CC(I/O)_AUX

V

DDA_AUX

V

DDA_AUX

2

73

18

43

58

16

11

25

40

55

71

3

77

98

100

86

93

GNDA

GNDA

GNDA

GNDA

GNDA

GNDD

GNDD

GNDD

GNDD

GNDD

GNDD

GNDD

GNDD

GNDA

GNDA

GNDA

GNDA

1

17

46

61

72

6

19

32

49

64

76

94

95

82

89

84

91

AD[31:0]

22 pF

22 pF

1 kΩ

R8

4.7 kΩ

4.7 kΩ

DV

AUX

DV

AUX

DV

AUX

A0

DV

AUX

DV

AUX

FB3

BLM18PG121SN1

C18

0.001 μF

FB3 is optional. Can be directly tied to ground.

Fig 2. ISP1562 eval board schematic – ISP1562

NXP Semiconductors

Designing a Hi-Speed USB host PCI adapter using ISP1562/63

AN10050

Application note

A

N10050

_

4

Rev. 04 — 1 November 2007

11 of 18

© NXP B.V. 2007. All rights reserved.

INTA#

INTA#

INTA#

3.3 VAUX

RST#

RST#

RST#

GNT#

GNT#

GNT#

PME#

PME#

PME#

AD30

AD28

AD26

AD24

IDSEL

IDSEL

IDSEL

AD22

AD20

AD18

AD16

FRAME#

FRAME#

TRDY#

TRDY#

TRDY#

STOP#

STOP#

STOP#

PA R

PA R

PA R

AD15

AD13

AD11

AD9

C/BE0#

C/BE0#

C/BE0#

AD6

AD4

AD2

AD0

+5 V

+3.3 V

+

C52

47 μF / 10 V

47 μF / 10 V

C48

+

+

C58

47 μF / 6.3 V

C57

47 μF / 6.3 V

+

C16

0.1 μF

C53

0.1 μF

C54

1 nF

C64

100 pF

C15

0.1 μF

C14

0.1 μF

C47

1 nF

C46

1 nF

GND

PCICLK

PCICLK

PCICLK

REQ#

REQ#

REQ#

AD31

AD29

AD27

AD25

C/BE3#

C/BE3#

C/BE3#

AD23

AD21

AD19

AD17

C/BE2#

C/BE2#

C/BE2#

IRDY#

IRDY#

IRDY#

DEVSEL#

DEVSEL#

DEVSEL#

PERR#

PERR#

PERR#

SERR#

SERR#

SERR#

C/BE1#

C/BE1#

C/BE1#

AD14

AD12

AD10

AD8

AD7

AD5

AD3

AD1

GND

AD[31:0]

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

CON5

−12 V

TCK

GND

TDO

+5 V

+5 V

INTB

INTD

PRSNT 1

RESERVED

PRSNT2

TRST

+12 V

TMS

TDI

+5 V

INTA

INTC

+5 V

RESERVED

VIO

RESERVED

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

RESERVED

GND

CLK

GND

REQ

VIO

AD31

AD29

GND

AD27

AD25

3V3

C/BE3

AD23

GND

AD21

AD19

3V3

AD17

C/BE2

GND

IRDY

3V3

DEVSEL

GND

LOCK

PERR

3V3

SERR

3V3

C/BE1

AD14

GND

AD12

AD10

M66EN

A14

A16

A17

A18

A19

A20

A21

A23

A25

A26

A27

A28

A29

A22

A24

A15

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

3V3_AUX

RST

VIO

GNT

GND

PME

AD30

3V3

AD28

AD26

GND

AD24

IDSEL

3V3

AD22

AD20

GND

AD18

AD16

3V3

FRAME

GND

TRDY

GND

STOP

3V3

RESERVED

RESERVED

GND

PA R

AD15

3V3

AD13

AD11

GND

AD9

AD8

AD7

3V3

AD5

AD3

GND

AD1

VIO

ACK64

+5V

+5V

C/BE0

3V3

AD6

AD4

GND

AD2

AD0

VIO

REQ64

+5V

+5V

PCIBUS

Fig 3. ISP1562 eval board schematic – PCI edge connector

NXP Semiconductors

Designing a Hi-Speed USB host PCI adapter using ISP1562/63

AN10050

Application note

A

N10050

_

4

Rev. 04 — 1 November 2007

12 of 18

© NXP B.V. 2007. All rights reserved.

D

VAUX

R11

10 kΩ

R12

10 kΩ

10 kΩ

R9

R10

10 kΩ

C39

0.1 μF

C40

0.1 μF

R13

10 kΩ

10 kΩ

R14

560 Ω

R21

PWE1#

PWE1#

OC1#

OC1#

OC2#

OC2#

PWE2#

PWE2#

U3

4

3

2

1

MIC2526

ENB#

FLGB#

FLGA#

ENA#

OUTB

GND

IN

OUTA

FB9

BLM31PG121SN1

FB10

BLM31PG121SN1

+5 V_Standby

C11

0.1 μF

C12

0.1 nF

+

C13

100 μF / 10 V

Optional

J1

1

2

3

+5 V

BUS

C5

47 μF / 10 V

C7

0.1 μF

C6

100 pF

5

6

7

8

R20

560 Ω

LED

D2

C1

0.01 μF

C2

47 μF / 10 V

+

C3

1 nF

+

C4

22 μF / 10 V

C41

0.1 μF

+5 V

BUS

FB8

BLM41PG600SN1

D1

LED

+5V_Standby

A

TT1

TT2

B

+5 V

C42

0.1 μF

C55

220 μF / 10 V

+

C43

1 nF

C

1

4

5

6

2

3

FB4

BLM18PG121SN1

V

BUS

GND

SHIELD

SHIELD

D−

D+

CON1

USB1

IP 4220CZ6

1

2

3

4

6

5

ESD1

DM1

DM1

DP1

DP2

R24

15 kΩ

R25

15 kΩ

DP1

C44

0.1 μF

C56

220 μF / 10 V

+

C45

1 nF

FB5

BLM18PG121SN1

V

BUS

GND

SHIELD

SHIELD

D−

D+

CON2

USB2

1

4

6

2

3

5

1

2

3

4

5

6

IP 4220CZ6

ESD2

R26

15 kΩ

R27

15 kΩ

DM2

DM2

DP2

Bracket holes

SW1

SOCKET

SW2

SOCKET

+

D

VAUX

Fig 4. ISP1562 eval board schematic – port power control and ESD protection

NXP Semiconductors

AN10050

Designing a Hi-Speed USB host PCI adapter using ISP1562/63

AN10050_4 © NXP B.V. 2007. All rights reserved.

Application note Rev. 04 — 1 November 2007 13 of 18

PCI

PCICONN.SCH

AD[31:0]

PCICLK

IDSEL

C/BE0#

C/BE1#

C/BE2#

C/BE3#

INTA#

REQ#

FRAME#

TRDY#

IRDY#

DEVSEL#

STOP#

PERR#

SERR#

PAR

PME#

PWE3#

PWE4#

DM1

DM2

DP2

ISP1563_ES1

ISP1563_ES1.SCH

POWER_SWITCH

POWER_SWITCH.SCH

RST#

GNT#

AD[31:0]

PCICLK

IDSEL

C/BE0#

C/BE1#

C/BE2#

C/BE3#

INTA#

REQ#

FRAME#

TRDY#

IRDY#

DEVSEL#

STOP#

PERR#

SERR#

PAR

PME#

RST#

GNT#

OC1#

OC2#

OC3#

OC4#

PWE1#

PWE2#

DP1

DM3

DP3

DP4

PWE3#

PWE4#

DM1

DM2

DP2

OC1#

OC2#

OC3#

OC4#

PWE1#

PWE2#

DP1

DM3

DP3

DP4

DM4

DM4

Fig 5. ISP1563 eval board schematic – top-level interfaces

NXP Semiconductors

Designing a Hi-Speed USB host PCI adapter using ISP1562/63

AN10050

Application note

A

N10050

_

4

Rev. 04 — 1 November 2007

14 of 18

© NXP B.V. 2007. All rights reserved.

C17

0.1 μF

C48

C19

+3.3 V

C49

Should be placed

as close as

possible to pin 95

Should be placed

as close as

possible to pin 67

C18

0.1 μF

1 nF

0.1 μF

1 nF

All capacitors should be placed as close as possible

to the corresponding power pins.

+3.3 V

C51

1 nF

C52

1 nF

C53

1 nF

C29

C30

C31

0.1 μF

0.1 μF

0.1 μF

0.1 μF

C32

C33

C34

C35

0.1 μF

0.1 μF

0.1 μF

Should be placed as close as

possible to pin 12

C36

0.1 μF

SCL

SDA

+3.3 V

C27

0.1 μF

1

2

3

4

6

8

5

7

U4A

A1

A3

VCC

NC/WP

SCL

SDA

AT24C01A-2.7

AT24C01A-2.7

A0

A1

A3

VCC

NC/WP

SCL

SDA

U4

1

2

3

4

6

8

7

5

R35

0 Ω

R46

0 Ω

DV

AUX

R25

R26

4.7 kΩ

4.7 kΩ

R34

0 Ω

DV

AUX

R28

51 kΩ

R33

0 Ω

SEL48M

121

122

123

SCL

SDA

SEL48M

C20 C21

C22

C68 C23

C24

0.1 μF

0.1 μF

4.7 μF

4.7 μF

C69

0.1 μF

+

0.1 μF

0.1 μF

+

JP1

HEADER 3

3.3 V

AUX

1

2

3

BLM21PG221SN1

C25

C70

C67

0.1 μF

470pF

47 μF / 6.3 V

D5

LED

R41

330 Ω

+

FB 10

All capacitors should be

placed as close as possible

to the corresponding ferrite

AV

AUX

BLM18PG121SN1

FB6

C26

C50

0.1 μF

1 nF

C71

+

4.7 μF/ 6.3 V

+3.3 V

DV

AUX

AV

AUX

AD0

AD1

AD2

AD4

AD3

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

AD[0]

AD[1]

AD[2]

AD[3]

AD[4]

AD[5]

AD[6]

AD[7]

AD[8]

AD[9]

AD[10]

AD[11]

AD[12]

AD[13]

AD[14]

AD[15]

AD[16]

AD[17]

AD[18]

AD[19]

AD[20]

AD[21]

AD[22]

AD[23]

AD[24]

AD[25]

AD[26]

AD[27]

AD[28]

AD[29]

AD[30]

AD[31]

AD[31:0]

C/BE0#

C/BE1#

C/BE2#

C/BE3#

C/BE0#

C/BE1#

C/BE2#

C/BE3#

C/BE#[0]

C/BE#[1]

C/BE#[2]

C/BE#[3]

PCICLK

IDSEL

GNT#

AMB1

INTA#

REQ#

FRAME#

TRDY#

IRDY#

DEVSEL#

STOP#

PERR#

SERR#

PAR

PME#

RST#

CLKRUN#

AMB2

AMB3

AMB4

GRN1

GRN2

GRN3

GRN4

OC1_N

OC2_N

OC3_N

OC4_N

PWE1_N

PWE2_N

PWE3_N

PWE4_N

DM1

DM2

DM3

DM4

OC1#

OC2#

OC3#

OC4#

93

91

89

63

DM1

DM2

DM3

DM4

GRN1

GRN2

GRN3

GRN4

AMB1

AMB2

PWE1#

PWE2#

PWE3#

PWE4#

94

92

90

64

97

106

113

115

96

105

112

114

101

108

117

125

DP1

DP2

DP3

DP4

DP1

DP2

DP3

DP4

103

110

119

127

R29

51 kΩ

R30

51 kΩ

R36

0 Ω

R37

0 Ω

OC1#

OC2#

OC3#

OC4#

PWE1#

PWE2#

PWE3#

PWE4#

DM1

DM2

DM3

DM4

DP1

DP2

DP3

DP4

RREF

GNDA

IDSEL

GNT#

INTA#

REQ#

FRAME#

TRDY#

IRDY#

DEVSEL#

STOP#

PERR#

SERR#

PAR

PCICLK

PME#

RST#

IDSEL

GNT#

INTA#

REQ#

FRAME#

TRDY#

IRDY#

DEVSEL#

STOP#

PERR#

SERR#

PAR

PCICLK

PME#

RST#

R42

1 kΩ

72

58

45

33

14

19

18

34

46

47

48

49

51

52

54

55

57

15

17

1

XTAL2

XTAL1

R44

99

98

86

87

12 kΩ / 1 %

FB7

BLM18PG121SN1

C73

22 pF

C72

22 pF

OSC1

12 MHz

R45

33Ω

DV

AUX

OSC2

48MHz

R38

0Ω

C74

2.2 μF / 10 V

0.1 μF

C28

14

8

7

1

IRQ12

IRQ1

IRQ12

IRQ1

A20OUT

KBIRQ1

MUIRQ12

SMI#

A20OUT

KBIRQ1

MUIRQ12

SMI#

3

4

7

8

9

13

SEL2PORTS

5

R27

DV

AUX

R31

R32

R39

R40

JP2

HEADER 4 X 2

1

2

3

4

5

7

6

8

DV

AUX

4.7 kΩ

R43

1kΩ

DV

AUX

DV

AUX

DV

AUX

AV

AUX

AUX1V8

AUX1V8

REG1V8

REG1V8

REG1V8

V

I(VREG3V3)

V

CC(I/O)

V

CC(I/O)

V

CC(I/O)

V

CC(I/O)

V

CC(I/O)

V

I(VAUX3V3)

V

CC(I/O)_AUX

V

CC(I/O)_AUX

V

DDA_AUX

V

DDA_AUX

V

DDA_AUX

V

DDA_AUX

DV

AUX

DV

AUX

DV

AUX

GNDA

GNDA

GNDA

GNDA

GNDA

GNDD

GNDD

GNDD

GNDD

GNDD

GNDD

GNDA

GNDA

GNDA

GNDA

GNDA

GNDA

GNDA

GNDA

GNDD

11

85

28

53

70

26

21

35

50

67

83

12

6

95

104

111

120

128

2

16

76

88

10

27

56

73

84

100

107

116

124

102

109

118

126

29

42

56

82

81

77

75

74

71

69

68

66

80

79

78

65

62

61

60

44

43

41

40

39

38

37

36

32

31

30

25

24

23

22

20

U3

ISP1563

+

GND

A0

GND

51 kΩ

51 kΩ

0 Ω

0 Ω

not to be implemented

FB7 is optional.

Can be directly

tied to ground.

Fig 6. ISP1563 eval board schematic – ISP1563

NXP Semiconductors

Designing a Hi-Speed USB host PCI adapter using ISP1562/63

AN10050

Application note

A

N10050

_

4

Rev. 04 — 1 November 2007

15 of 18

© NXP B.V. 2007. All rights reserved.

INTA#

INTA#

INTA#

3.3 V

AUX

RST#

RST#

RST#

GNT#

GNT#

GNT#

PME#

PME#

PME#

AD30

AD28

AD26

AD24

IDSEL

IDSEL

IDSEL

AD22

AD20

AD18

AD16

FRAME#

FRAME#

TRDY#

TRDY#

TRDY#

STOP#

STOP#

STOP#

PA R

PA R

PA R

AD15

AD13

AD11

AD9

C/BE0#

C/BE0#

C/BE0#

AD6

AD4

AD2

AD0

+5 V

+3.3 V

+

C75

47 μF / 10 V

47 μF / 10 V

C41

+

+

C65

47 μF / 6.3 V

C66

47 μF / 6.3 V

+

C16

0.1 μF

C76

0.1 μF

C77

1 nF

C63

100 pF

C15

0.1 μF

C14

0.1 μF

C47

1 nF

C46

1 nF

GND

PCICLK

PCICLK

PCICLK

REQ#

REQ#

REQ#

AD31

AD29

AD27

AD25

C/BE3#

C/BE3#

C/BE3#

AD23

AD21

AD19

AD17

C/BE2#

C/BE2#

C/BE2#

IRDY#

IRDY#

IRDY#

DEVSEL#

DEVSEL#

DEVSEL#

PERR#

PERR#

PERR#

SERR#

SERR#

SERR#

C/BE1#

C/BE1#

C/BE1#

AD14

AD12

AD10

AD8

AD7

AD5

AD3

AD1

GND

AD[31:0]

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

CON5

−12 V

TCK

GND

TDO

+5 V

+5 V

INTB

INTD

PRSNT 1

RESERVED

PRSNT2

TRST

+12 V

TMS

TDI

+5 V

INTA

INTC

+5 V

RESERVED

VIO

RESERVED

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

RESERVED

GND

CLK

GND

REQ

VIO

AD31

AD29

GND

AD27

AD25

3V3

C/BE3

AD23

GND

AD21

AD19

3V3

AD17

C/BE2

GND

IRDY

3V3

DEVSEL

GND

LOCK

PERR

3V3

SERR

3V3

C/BE1

AD14

GND

AD12

AD10

M66EN

A14

A16

A17

A18

A19

A20

A21

A23

A25

A26

A27

A28

A29

A22

A24

A15

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

3V3_AUX

RST

VIO

GNT

GND

PME

AD30

3V3

AD28

AD26

GND

AD24

IDSEL

3V3

AD22

AD20

GND

AD18

AD16

3V3

FRAME

GND

TRDY

GND

STOP

3V3

RESERVED

RESERVED

GND

PA R

AD15

3V3

AD13

AD11

GND

AD9

AD8

AD7

3V3

AD5

AD3

GND

AD1

VIO

ACK64

+5V

+5V

C/BE0

3V3

AD6

AD4

GND

AD2

AD0

VIO

REQ64

+5V

+5V

PCIBUS

FRAME#

Fig 7. ISP1563 eval board schematic – PCI edge connector

NXP Semiconductors

Designing a Hi-Speed USB host PCI adapter using ISP1562/63

AN10050

Application note

A

N10050

_

4

Rev. 04 — 1 November 2007

16 of 18

© NXP B.V. 2007. All rights reserved.

D

VAUX

R3

10 kΩ

R4

10 kΩ

10 kΩ

R1

R2

10 kΩ

C1

0.1 μF

C2

0.1 μF

R5

10 kΩ

10 kΩ

R7

560 Ω

R14

PWE1#

PWE1#

OC1#

OC1#

OC2#

OC2#

PWE2#

PWE2#

U3

4

3

2

1

MIC2526

ENB#

FLGB#

FLGA#

ENA#

OUTB

GND

IN

OUTA

FB8

BLM31PG121SN1

FB9

BLM31PG121SN1

+5 V_Standby

C13

0.1 μF

C45

0.1 nF

+

C64

100 μF / 10 V

Optional

J1

1

2

3

+5 V

BUS

C39

47 μF / 10 V

C5

0.1 μF

C6

0.1 μF

5

6

7

8

R13

560 Ω

LED

D2

C37

0.01 μF

C38

47 μF / 10 V

+

C42

1 nF

+

C54

22 μF / 10 V

C3

0.1 μF

+5 V

BUS

FB1

BLM41PG600SN1

D1

LED

+5V_Standby

A

TT1

TT2

B

+5 V

C4

0.1 μF

C55

220 μF / 10 V

+

C43

1 nF

C

1

4

5

6

2

3

FB2

BLM18PG121SN1

V

BUS

GND

SHIELD

SHIELD

D−

D+

CON1

USB1

IP 4220CZ6

1

2

3

4

6

5

ESD1

DM1

DM1

DP1

DP2

R17

15 kΩ

R18

15 kΩ

DP1

C7

0.1 μF

C56

220 μF / 10 V

+

C44

1 nF

FB3

BLM18PG121SN1

V

BUS

GND

SHIELD

SHIELD

D−

D+

CON2

USB2

1

4

6

2

3

5

1

2

3

4

5

6

IP 4220CZ6

ESD2

R19

15 kΩ

R20

15 kΩ

DM2

DM2

DP2

SW1

SOCKET

SW2

SOCKET

+

D

VAUX

D

VAUX

R6

10 kΩ

R8

10 kΩ

10 kΩ

R9

R10

10 kΩ

C8

0.1 μF

C9

0.1 μF

R12

10 kΩ

10 kΩ

R11

560 Ω

R16

PWE3#

PWE3#

OC3#

OC3#

OC4#

OC4#

PWE4#

PWE4#

U2

4

3

2

1

MIC2526

ENB#

FLGB#

FLGB#

ENA#

OUTB

IN

GND

OUTB

5

7

6

8

R15

560 Ω

LED

D4

C10

0.1 μF

D3

LED

C11

0.1 μF

C57

220 μF / 10 V

+

C61

1 nF

1

4

5

6

2

3

FB4

BLM18PG121SN1

V

BUS

GND

SHIELD

SHIELD

D−

D+

CON3

USB3

IP 4220CZ6

1

2

3

4

6

5

ESD3

DM3

DM3

DP3

DP4

R21

15 kΩ

R22

15 kΩ

DP3

C12

0.1 μF

C58

220 μF / 10 V

+

C62

1 nF

FB5

BLM18PG121SN1

V

BUS

GND

SHIELD

SHIELD

D−

D+

CON4

USB2

1

4

6

2

3

5

1

2

3

4

5

6

IP 4220CZ6

ESD4

R23

15 kΩ

R24

15 kΩ

DM4

DM4

DP4

D

VAUX

C59

100 pF

+

C40

47 μF / 10 V

C60

100 pF

Bracket holes

Fig 8. ISP1563 eval board schematic – port power control and ESD protection

NXP Semiconductors

AN10050

Designing a Hi-Speed USB host PCI adapter using ISP1562/63

AN10050_4 © NXP B.V. 2007. All rights reserved.

Application note Rev. 04 — 1 November 2007 17 of 18

6. Legal information

6.1 Definitions

Draft — The document is a draft version only. The content is still under

internal review and subject to formal approval, which may result in

modifications or additions. NXP Semiconductors does not give any

representations or warranties as to the accuracy or completeness of

information included herein and shall have no liability for the consequences

of use of such information.

6.2 Disclaimers

General — Information in this document is believed to be accurate and

reliable. However, NXP Semiconductors does not give any representations

or warranties, expressed or implied, as to the accuracy or completeness of

such information and shall have no liability for the consequences of use of

such information.

Right to make changes — NXP Semiconductors reserves the right to make

changes to information published in this document, including without

limitation specifications and product descriptions, at any time and without

notice. This document supersedes and replaces all information supplied prior

to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed,

authorized or warranted to be suitable for use in medical, military, aircraft,

space or life support equipment, nor in applications where failure or

malfunction of a NXP Semiconductors product can reasonably be expected

to result in personal injury, death or severe property or environmental

damage. NXP Semiconductors accepts no liability for inclusion and/or use of

NXP Semiconductors products in such equipment or applications and

therefore such inclusion and/or use is for the customer’s own risk.

Applications — Applications that are described herein for any of these

products are for illustrative purposes only. NXP Semiconductors makes no

representation or warranty that such applications will be suitable for the

specified use without further testing or modification.

6.3 Trademarks

Notice: All referenced brands, product names, service names and

trademarks are property of their respective owners.

I

2

C-bus — logo is a trademark of NXP B.V.

NXP Semiconductors

AN10050

Designing a Hi-Speed USB host PCI adapter using ISP1562/63

Please be aware that important notices concerning this document and the product(s)

described herein, have been included in the section 'Legal information'.

© NXP B.V. 2007. All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, email to: salesad[email protected]

Date of release: 1 November 2007

Document identifier: AN10050_4

7. Contents

1. Introduction .........................................................3

2. ISP1562/3 initialization........................................3

3. Description of the application schematics........4

3.1 Distribution of power sources and power

management support .........................................

4

3.2 Input clock: applies only to the ISP1563................5

3.3 Selecting the number of ports: applies only to the

ISP1563 .............................................................

5

3.4 Subsystem vendor ID and subsystem device ID...5

3.5 Legacy support: applies only to the ISP1563 ........6

3.6 Overcurrent protection...........................................6

4. PCB design recommendations ..........................7

5. Schematics ..........................................................8

6. Legal information..............................................17

6.1 Definitions............................................................17

6.2 Disclaimers..........................................................17

6.3 Trademarks.........................................................17

7. Contents.............................................................18

/