Intel MFS5000SIB Datasheet

- Category

- Server barebones

- Type

- Datasheet

This manual is also suitable for

Intel

®

Compute Module MFS5000SI

Technical Product Specification

Intel order number: E15154-007

Revision 1.4

June 2009

Enterprise Platforms and Services Division

Revision History Intel® Compute Module MFS5000SI TPS

Revision History

Date Revision

Number

Modifications

July 2007 0.95 Initial release.

August 2007 0.96 Updated

September 2007 1.0 Updated

February 2008 1.1 Updated

November 2008 1.2 Updated

May 2009 1.3 Updated

June 2009 1.4 Updated supported memory configurations

Disclaimers

Information in this document is provided in connection with Intel

®

products. No license, express or

implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except

as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel

products including liability or warranties relating to fitness for a particular purpose, merchantability, or

infringement of any patent, copyright or other intellectual property right. Intel products are not intended for

use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and

product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked

"reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility

whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel

®

Compute Module MFS5000SI may contain design defects or errors known as errata which may

cause the product to deviate from published specifications. Current characterized errata are available on

request.

Intel Corporation server baseboards support peripheral components and contain a number of high-

density VLSI and power delivery components that need adequate airflow to cool. Intel’s own chassis are

designed and tested to meet the intended thermal requirements of these components when the fully

integrated system is used together. It is the responsibility of the system integrator that chooses not to use

Intel developed server building blocks to consult vendor datasheets and operating parameters to

determine the amount of air flow required for their specific application and environmental conditions. Intel

Corporation can not be held responsible if components fail or the compute module does not operate

correctly when used outside any of their published operating or non-operating limits.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation.

*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2007-2009.

Revision 1.4

Intel order number: E15154-007

ii

Intel® Compute Module MFS5000SI TPS Table of Contents

Table of Contents

1. Introduction.............................................................................................................................1

1.1 Chapter Outline........................................................................................................ 1

1.2 Intel

®

Compute Module Use Disclaimer................................................................... 1

2. Product Overview....................................................................................................................2

2.1 Intel

®

Compute Module MFS5000SI Feature Set .................................................... 2

2.2 Compute Module Layout.......................................................................................... 3

2.2.1 Connector and Component Locations ..................................................................... 3

2.2.2 External I/O Connector Locations............................................................................ 4

2.2.3 Compute Module Mechanical Drawings .................................................................. 5

3. Functional Architecture ...........................................................................................................6

3.1 Intel

®

5000P Memory Controller Hub (MCH) ........................................................... 7

3.1.1 System Bus Interface............................................................................................... 7

3.1.2 Processor Support ................................................................................................... 7

3.1.3 Memory Subsystem ................................................................................................. 8

3.2 Intel

®

6321ESB I/O Controller Hub ........................................................................ 16

3.2.1 PCI Subsystem ...................................................................................................... 16

3.2.2 Serial ATA Support ................................................................................................ 17

3.2.3 Parallel ATA (PATA) Support ................................................................................ 17

3.2.4 USB 2.0 Support.................................................................................................... 18

3.3 Video Support ........................................................................................................ 18

3.4 Network Interface Controller (NIC) ........................................................................ 19

3.4.1 Intel

®

I/O Acceleration Technology ........................................................................ 19

3.4.2 MAC Address Definition......................................................................................... 19

3.5 Super I/O ............................................................................................................... 19

4. Connector / Header Locations and Pin-outs............................................................................21

4.1 Board Connector Information................................................................................. 21

4.2 Power Connectors ................................................................................................. 21

4.3 I/O Connector Pin-out Definition ............................................................................ 22

4.3.1 VGA Connector...................................................................................................... 22

4.3.2 I/O Mezzanine Card Connector ............................................................................. 22

4.3.3 Midplane Signal Connector.................................................................................... 23

Revision 1.4 iii

Intel order number: E15154-007

Table of Contents Intel® Compute Module MFS5000SI TPS

4.3.4 Serial Port Connector ............................................................................................ 24

4.3.5 USB 2.0 Connectors .............................................................................................. 25

5. Jumper Block Settings ............................................................................................................26

5.1 Recovery Jumper Blocks ....................................................................................... 26

5.1.1 CMOS Clear and Password Reset Usage Procedure ........................................... 27

5.1.2 BMC Force Update Procedure .............................................................................. 27

5.1.3 System Status LED – BMC Initialization................................................................ 28

6. Product Regulatory Requirements .........................................................................................29

6.1 Product Regulatory Requirements......................................................................... 29

6.2 Product Regulatory Compliance and Safety Markings .......................................... 29

6.3 Product Environmental/Ecology Requirements ..................................................... 29

6.4 Product Environmental/Ecology Markings ............................................................. 29

Appendix A: Integration and Usage Tips .......................................................................................30

Appendix B: BMC Sensor Tables....................................................................................................31

Appendix C: POST Error Messages and Handling ...........................................................................37

Appendix D: Supported Intel

®

Modular Server System....................................................................40

Glossary.......................................................................................................................................41

Reference Documents..................................................................................................................44

Revision 1.4

Intel order number: E15154-007

iv

Intel® Compute Module MFS5000SI TPS List of Figures

List of Figures

Figure 1. Component and Connector Location Diagram ..............................................................3

Figure 2. Intel

®

Compute Module MFS5000SI Front Panel Layout............................................... 4

Figure 3. Intel

®

Compute Module MFS5000SI – Hole and Component Positions ........................ 5

Figure 4. Compute Module Functional Block Diagram .................................................................6

Figure 5. CEK Processor Mounting ..............................................................................................8

Figure 6. Memory Layout .............................................................................................................. 9

Figure 7. Recommended Minimum Two-DIMM Memory Configuration ...................................... 12

Figure 8. Recommended Four-DIMM Configuration................................................................... 13

Figure 9. Single Branch Mode Sparing DIMM Configuration ...................................................... 14

Figure 10. Recovery Jumper Blocks ........................................................................................... 26

Figure 11. Intel

®

Modular Server System MFSYS25 ..................................................................40

Revision 1.4 v

Intel order number: E15154-007

List of Tables Intel® Compute Module MFS5000SI TPS

Revision 1.4

Intel order number: E15154-007

vi

List of Tables

Table 1. I

2

C Addresses for Memory Module SMB ........................................................................ 9

Table 2. Maximum 8-DIMM System Memory Configuration – x8 Single Rank ........................... 10

Table 3. Maximum 8-DIMM System Memory Configuration – x4 Dual Rank.............................. 10

Table 4. PCI Bus Segment Characteristics................................................................................. 16

Table 5. Video Modes ................................................................................................................. 18

Table 6. Serial Header Pin-out.................................................................................................... 20

Table 7. Board Connector Matrix ................................................................................................ 21

Table 8. Power Connector Pin-out (J1A1) .................................................................................. 21

Table 9. VGA Connector Pin-out (J6A1)..................................................................................... 22

Table 10. 120-pin I/O Mezzanine Card Connector Pin-out ......................................................... 22

Table 11. 96-pin Midplane Signal Connector Pin-out ................................................................. 23

Table 12. Internal 9-pin Serial ‘A’ Header Pin-out (J1B1) ........................................................... 25

Table 13. External USB Connector Pin-out ................................................................................25

Table 14. Recovery Jumpers ......................................................................................................27

Table 15. BMC Sensors.............................................................................................................. 32

Table 16. Analog Sensor Thresholds.......................................................................................... 36

Table 17. POST Error Messages and Handling.......................................................................... 37

Table 18. POST Error Beep Codes ............................................................................................39

Intel® Compute Module MFS5000SI TPS 0BIntroduction

1. Introduction

This Technical Product Specification (TPS) provides board-specific information detailing the features,

functionality, and high-level architecture of the Intel

®

Compute Module MFS5000SI. The Intel

®

5000

Series Chipsets Server Board Family Datasheet should also be referenced for more in-depth detail of

various board subsystems, including chipset, BIOS, System Management, and System Management

software.

1.1 Chapter Outline

This document is divided into the following chapters:

Chapter 1 – Introduction

Chapter 2 – Product Overview

Chapter 3 – Functional Architecture

Chapter 4 – Connector / Header Locations and Pin-outs

Chapter 5 – Jumper Block Settings

Chapter 6 – Product Regulatory Requirements

Appendix A – Integration and Usage Tips

Appendix B – BMC Sensor Tables

Appendix C – Post Error Messages and Handling

Appendix D – Supported Intel

®

Modular Server System

1.2 Intel

®

Compute Module Use Disclaimer

Intel

®

Modular Server components require adequate airflow to cool. Intel ensures through its own chassis

development and testing that when these components are used together, the fully integrated system will

meet the intended thermal requirements. It is the responsibility of the system integrator who chooses not

to use Intel-developed server building blocks to consult vendor datasheets and operating parameters to

determine the amount of airflow required for their specific application and environmental conditions. Intel

Corporation cannot be held responsible if components fail or the system does not operate correctly when

used outside any of their published operating or non-operating limits.

Revision 1.4 1

Intel order number: E15154-007

1BProduct Overview Intel® Compute Module MFS5000SI TPS

2. Product Overview

The Intel

®

Compute Module MFS5000SI is a monolithic printed circuit board with features that were

designed to support the high-density compute module market.

2.1 Intel

®

Compute Module MFS5000SI Feature Set

Feature Description

Processors 771-pin LGA sockets supporting one or two Dual-Core or Quad-Core Intel

®

Xeon

®

processors 5000 sequence, with system bus speeds of 1066 MHz or 1333 MHz

Memory 8 keyed DIMM slots supporting fully buffered DIMM technology (FBDIMM) memory.

240-pin DDR2-677 FBDIMMs must be used.

Chipset Intel

®

5000 Chipset family, which includes the following components:

Intel

®

5000P Memory Controller Hub

Intel

®

6321ESB I/O Controller Hub

On-board

Connectors/Headers

External connections:

Two USB 2.0 ports

Video connector

Internal connectors/headers:

One DH-10 Serial A debug header

One Intel

®

I/O Mezzanine Connector supporting Dual Gigabit NIC Intel

®

I/O

Expansion Module (Optional)

On-board Video ATI* ES1000 video controller with 16MB DDR SDRAM

On-board Hard Drive

Controller

LSI* 1064e SAS controller

LAN Two integrated 10/100/1000 Ethernet ports and two optional 10/100/1000 Ethernet

ports, provided by the Dual Gigabit NIC mezzanine module

Revision 1.4

Intel order number: E15154-007

2

Intel® Compute Module MFS5000SI TPS 1BProduct Overview

2.2 Compute Module Layout

2.2.1 Connector and Component Locations

The following figure shows the board layout of the Intel

®

Compute Module MFS5000SI. Each connector

and major component is identified by a number or letter. A description of each identified item is provided

below the figure.

Description Description

A Midplane Power Connector B Midplane Signal Connector

C POST Code Diagnostic LEDs D SAS Controller

E FBDIMM Slots F Intel

®

5000P Memory Controller Hub (MCH)

G CPU #1 Socket H Voltage Regulator Heatsink

I Power/Fault LEDs J Power Button

K Activity and ID LEDs L Video Connector

M USB1 and USB2 Connectors N CPU #2 Socket

O Intel® 6321ESB I/O Controller Hub P CMOS Battery

Q I/O Mezzanine Card Connector

Figure 1. Component and Connector Location Diagram

Revision 1.4 3

Intel order number: E15154-007

1BProduct Overview Intel® Compute Module MFS5000SI TPS

2.2.2 External I/O Connector Locations

The following drawing shows the layout of the external I/O components for the Intel

®

Compute Module

MFS5000SI.

A USB ports 1 and 2 E Hard Drive Activity LED

B Video F ID LED

C I/O ports 1 and 2 G Power button

D NIC ports 1 and 2 H Power and Fault LEDs

Figure 2. Intel

®

Compute Module MFS5000SI Front Panel Layout

Revision 1.4

Intel order number: E15154-007

4

Intel® Compute Module MFS5000SI TPS 1BProduct Overview

Revision 1.4 5

2.2.3 Compute Module Mechanical Drawings

Figure 3. Intel

®

Compute Module MFS5000SI – Hole and Component Positions

Intel order number: E15154-007

2BFunctional Architecture Intel® Compute Module MFS5000SI TPS

3. Functional Architecture

The architecture and design of the Intel

®

Compute Module MFS5000SI is based on the Intel

®

5000

Chipset Family. The chipset is designed for systems based on the Dual-Core and Quad-Core Intel

®

Xeon

®

processor 5000 sequence with system bus speeds of 667 MHz, 1066 MHz, and 1333 MHz. The

chipset is made up of two main components: the Memory Controller Hub (MCH) for the host bridge and

the Intel

®

6321ESB I/O controller hub for the I/O subsystem. This chapter provides a high-level

description of the functionality associated with each chipset component and the architectural blocks that

make up the server board. For more in-depth detail of the functionality for each

of the chipset

components and each of the functional architecture blocks, see the Intel

®

5000 Series Chipsets Server

Board Family Datasheet.

Figure 4. Compute Module Functional Block Diagram

Note: The previous diagram uses the Intel

®

5000P MCH as a general reference designator for MCH

components supported on this server board.

Revision 1.4

Intel order number: E15154-007

6

Intel® Compute Module MFS5000SI TPS 2BFunctional Architecture

3.1 Intel

®

5000P Memory Controller Hub (MCH)

This section describes the general functionality of the memory controller hub as it is implemented on this

server board.

The MCH is a single 1432-pin FCBGA package, which includes the following core platform functions:

System Bus Interface for the processor subsystem

Memory Controller

PCI Express* Ports, including the Enterprise South Bridge Interface (ESI)

FBD Thermal Management

SMBus Interface

Additional information about MCH functionality can be obtained from the Intel

®

5000 Series Chipsets

Server Board Family Datasheet and the Intel

®

5000P Memory Controller Hub External Design

Specification.

3.1.1 System Bus Interface

The MCH is configured for symmetric multi-processing across two independent front-side bus interfaces

that connect to the Dual-Core and Quad-Core Intel

®

Xeon

®

processors 5000 sequence. Each front-side

bus on the MCH uses a 64-bit wide 1066 or 1333 MHz data bus. The 1333-MHz data bus is capable of

transferring data at up to 10.66 GB/s. The MCH supports a 36-bit wide address bus, capable of

addressing up to 64 GB of memory. The MCH is the priority agent for both front-side bus interfaces, and

is optimized for one processor on each bus.

3.1.2 Processor Support

The Intel

®

Compute Module MFS5000SI supports one or two Dual-Core Intel

®

Xeon

®

processors 5100

sequence or Quad-Core Intel

®

Xeon

®

processors 5300 and 5400 sequence with system bus speeds of

1066 MHz and 1333 MHz. Previous generations of the Intel

®

Xeon

®

processor are not supported in the

Intel

®

Compute Module MFS5000SI. To see a list of the latest processors that have been validated on

this product, refer to

http://support.intel.com/support/motherboards/server/MFS5000SI/ and select

the Supported Processors List.

3.1.2.1 Processor Population Rules

When two processors are installed, both must be of identical revision, core voltage, and bus/core speed.

Mixed processor steppings is supported in N and N-1 configurations only. When only one processor is

installed, it must be in the socket labeled CPU1. The other socket must be empty.

The board is designed to provide up to 115 A of current per processor. Processors with higher current

requirements are not supported.

When using a single processor configuration, a terminator is not required in the second processor socket.

Revision 1.4 7

Intel order number: E15154-007

2BFunctional Architecture Intel® Compute Module MFS5000SI TPS

3.1.2.2 Common Enabling Kit (CEK) Design Support

The compute module complies with Intel’s Common Enabling Kit (CEK) processor mounting and heatsink

retention solution. The compute module ships with a CEK spring snapped onto the underside of the

server board, beneath each processor socket. The heatsink attaches to the CEK, over the top of the

processor and the thermal interface material (TIM). For the stacking order of the chassis, CEK spring,

server board, TIM, and heatsink, see the following figure.

The CEK spring is removable, allowing for the use of non-Intel heatsink retention solutions.

Note: The processor heatsink and CEK spring shown in the following diagram are for reference purposes

only. The actual processor heatsink and CEK solutions compatible with this generation server board may

be of a different design.

Heatsink assembly

Thermal interface material (TIM)

Server board

CEK spring

Chassis

Figure 5. CEK Processor Mounting

3.1.3 Memory Subsystem

The MCH masters four fully buffered DIMM (FBD) memory channels. FBD memory utilizes a narrow high-

speed frame-oriented interface referred to as a channel. The four FBD channels are organized into two

branches of two channels per branch. Each branch is supported by a separate memory controller. The

two channels on each branch operate in lock step to increase FBD bandwidth. On the server board, the

four channels are routed to eight DIMM slots and are capable of supporting registered DDR2-533 and

DDR2-667 FBDIMM memory (stacked or unstacked). Peak theoretical memory data bandwidth is 6.4

GB/s with DDR2-533 and 8.0 GB/s with DDR2-667.

On the Intel

®

Compute Module MFS5000SI, a pair of channels becomes a branch where Branch 0

consists of channels A and B, and Branch 1 consists of channels C and D. FBD memory channels are

organized into two branches for RAID 1 (mirroring) support.

Revision 1.4

Intel order number: E15154-007

8

Intel® Compute Module MFS5000SI TPS 2BFunctional Architecture

Revision 1.4 9

Intel order number: E15154-007

TP02299

DIMM D2

DIMM D1

DIMM C2

DIMM C1

DIMM B2

DIMM B1

DIMM A2

DIMM A1

Branch 0

MCH

Channel A

Channel B

Channel D

Channel C

Branch 1

Figure 6. Memory Layout

To boot the system, the system BIOS on the server board uses a dedicated I

2

C bus to retrieve DIMM

information needed to program the MCH memory registers. The following table provides the I

2

C

addresses for each DIMM slot.

Table 1. I

2

C Addresses for Memory Module SMB

Device Address

DIMM A1 0xA0

DIMM A2 0xA2

DIMM B1 0xA0

DIMM B2 0xA2

DIMM C1 0xA0

DIMM C2 0xA2

DIMM D1 0xA0

DIMM D2 0xA2

3.1.3.1 Memory RASUM Features

1

The MCH supports several memory RASUM (Reliability, Availability, Serviceability, Usability, and

Manageability) features. These features include the Intel

®

x4 Single Device Data Correction (Intel

®

x4

SDDC) for memory error detection and correction, Memory Scrubbing, Retry on Correctable Errors,

Memory Built In Self Test, DIMM Sparing, and Memory Mirroring. For more information regarding these

features, see the Intel

®

5000 Series Chipsets Server Board Family Datasheet.

1

DIMM Sparing and Memory Mirroring features will be made available post production launch with a BIOS update.

2BFunctional Architecture Intel® Compute Module MFS5000SI TPS

3.1.3.2 Supported and Nonsupported Memory Configurations

The server board design supports up to eight DDR2-533 or DDR2-667 Fully Buffered DIMMs (FBD

memory). Use of identical DIMMs with this server board is recommended. The following tables show the

maximum memory configurations supported using the specified memory technology.

Table 2. Maximum 8-DIMM System Memory Configuration – x8 Single Rank

DRAM Technology x8 Single

Rank

Maximum Capacity

Mirrored Mode

Maximum Capacity

Non-Mirrored Mode

256 Mb 1 GB 2 GB

512 Mb 2 GB 4 GB

1024 Mb 4 GB 8 GB

2048 Mb 8 GB 16 GB

Table 3. Maximum 8-DIMM System Memory Configuration – x4 Dual Rank

DRAM Technology x4 Dual

Rank

Maximum Capacity Mirrored

Mode

Maximum Capacity

Non-Mirrored Mode

256 Mb 4 GB 8 GB

512 Mb 8 GB 16 GB

1024 Mb 16 GB 32 GB

2048 Mb 16 GB 32 GB

The following configurations are not validated or supported with the Intel

®

Compute Module MFS5000SI:

DDR2 DIMMs that are not fully buffered are NOT supported on this server board.

DDR2-533 memory is not planned to be validated on this product.

Mixing memory type, size, speed, and/or rank is not validated and is not supported.

Mixing memory vendors is not validated and is not supported.

Non-ECC memory is not validated and is not supported in a server environment

For a complete list of supported memory for the Intel

®

Compute Module MFS5000SI, refer to the Tested

Memory List published in the Intel

®

Server Configurator Tool.

3.1.3.3 DIMM Population Rules and Supported DIMM Configurations

DIMM population rules depend on the operating mode of the memory controller, which is determined by

the number of DIMMs installed. DIMMs must be populated in pairs. DIMM pairs are populated in the

following DIMM slot order: A1 and B1, C1 and D1, A2 and B2, C2 and D2. DIMMs within a given pair

must be identical with respect to size, speed, and organization.

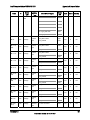

Intel supported DIMM configurations for this server board are shown in the following table.

Revision 1.4

Intel order number: E15154-007

10

Intel® Compute Module MFS5000SI TPS 2BFunctional Architecture

Supported and Validated configuration : Slot is populated

Supported but not validated configuration : Slot is

populated

Slot is not populated

Mirroring: Y = Yes and indicates that configuration supports Memory Mirroring.

Sparing: Y(x) = Yes and indicates that configuration supports Memory Sparing.

Where x = 0: Sparing supported on Branch0 only

1: Sparing supported on Branch1 only

0,1: Sparing supported on both branches

Branch 0 Branch 1

Channel A Channel B Channel C Channel D

DIMM_A1 DIMM_A2 DIMM_B1 DIMM B2 DIMM C1 DIMM C2 DIMM D1 DIMM D2

Mirroring

Possible

Sparing

Possible

Y (0)

Y

Y (0)

Y Y (0, 1)

Notes:

Single channel mode is only tested and supported with a 512-MB x8 FBDIMM installed in DIMM

slot A1.

The supported memory configurations must meet population rules defined above.

For best performance, the number of DIMMs installed should be balanced across both memory

branches. For example, a four-DIMM configuration will perform better than a two-DIMM

configuration and should be installed in DIMM slots A1, B1, C1, and D1. An eight-DIMM

configuration will perform better then a six-DIMM configuration.

Although mixed DIMM capacities (size, type, timing and/or rank) between channels is supported

by the memory controller, mixed DIMMs configurations are not validated or supported with the

Intel

®

Compute Module MFS5000SI. Refer to section 3.1.3.2 for supported and nonsupported

DIMM configuration information.

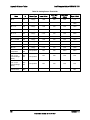

3.1.3.3.1 Minimum Non-Mirrored Mode Configuration

The server board is capable of supporting a minimum of one DIMM installed. However, for system

performance reasons, Intel’s recommendation is that at least 2 DIMMs be installed.

The following diagram shows the recommended minimum DIMM memory configuration. Populated DIMM

slots are shown in Grey.

Revision 1.4 11

Intel order number: E15154-007

2BFunctional Architecture Intel® Compute Module MFS5000SI TPS

TP02300

DIMM D2

DIMM D1

DIMM C2

DIMM C1

DIMM B2

DIMM B1

DIMM A2

DIMM A1

Branch 0

MCH

Channel A

Channel B

Channel D

Channel C

Branch 1

Figure 7. Recommended Minimum Two-DIMM Memory Configuration

Note: The server board supports single DIMM mode operation. Intel only validates and supports this

configuration with a single 512MB x8 FBDIMM installed in DIMM slot A1.

3.1.3.4 Non-mirrored Mode Memory Upgrades

The minimum memory upgrade increment is two DIMMs per branch. The DIMMs must cover the same

slot position on both channels. DIMM pairs must be identical with respect to size, speed, and

organization.

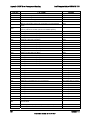

When adding two DIMMs to the configuration shown in Figure 7, the DIMMs should be populated in

DIMM slots C1 and D1 as shown in the following diagram. Populated DIMM slots are shown in Grey.

Revision 1.4

Intel order number: E15154-007

12

Intel® Compute Module MFS5000SI TPS 2BFunctional Architecture

TP02301

DIMM D2

DIMM D1

DIMM C2

DIMM C1

DIMM B2

DIMM B1

DIMM A2

DIMM A1

Branch 0

MCH

Channel A

Channel B

Channel D

Channel C

Branch 1

Figure 8. Recommended Four-DIMM Configuration

Functionally, DIMM slots A2 and B2 could also have been populated instead of DIMM slots C1 and D1.

However, your system will not achieve equivalent performance. Figure 8 shows the supported DIMM

configuration that is recommended because it allows both memory branches from the MCH to operate

independently and simultaneously. FBD bandwidth is doubled when both branches operate in parallel.

3.1.3.4.1 Mirrored Mode Memory Configuration

When operating in the mirrored mode, both branches operate in lock step. In mirrored mode, branch 1

contains a replicate copy of the data in branch 0. The minimum DIMM configuration to support memory

mirroring is four DIMMs, populated as shown in Figure 8. All four DIMMs must be identical with respect to

size, speed, and organization.

To upgrade a four-DIMM mirrored memory configuration, four additional DIMMs must be added to the

system. All four DIMMs in the second set must be identical to the first.

3.1.3.4.2 DIMM Sparing Mode Memory Configuration

The MCH provides DIMM sparing capabilities. Sparing is a RAS feature that involves configuring a DIMM

to be placed in reserve so it can be used to replace a DIMM that fails. DIMM sparing occurs within a

given bank of memory and is not supported across branches.

Two Memory Sparing configurations are supported:

Single Branch Mode Sparing

Dual Branch Mode Sparing

Revision 1.4 13

Intel order number: E15154-007

2BFunctional Architecture Intel® Compute Module MFS5000SI TPS

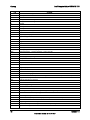

3.1.3.4.2.1 Single Branch Mode Sparing

Channel A Channel B Channel C Channel D

Branch 0 Branch 1

Intel® 5000P/5000X Memor

y

Controller Hub

Slot 1

Slot 2

DIMM_C2

DIMM_C1

DIMM_D2

DIMM_D1

DIMM_A1

DIMM_A2

DIMM_B1

DIMM_B2

Figure 9. Single Branch Mode Sparing DIMM Configuration

DIMM_A1 and DIMM_B1 must be identical in organization, size and speed.

DIMM_A2 and DIMM_B2 must be identical in organization, size and speed.

DIMM_A1 and DIMM_A2 should be identical in organization, size and speed. See note below.

DIMM_B1 and DIMM_B2 should be identical in organization, size and speed. See note below.

Sparing should be enabled in the BIOS setup.

The BIOS will configure Rank Sparing Mode.

The larger of the pairs {DIMM_A1, DIMM_B1} and {DIMM_A2, DIMM_B2} will be selected as the

spare pair unit.

Note: Use of identical memory is recommended with the Intel

®

Compute Module MFS5000SI. Mixing

memory type, size, speed, rank and/or vendors is not validated and is not supported with this product.

Refer to section 3.1.3.2 for supported and nonsupported memory features and configuration information.

3.1.3.4.2.2 Dual Branch Mode Sparing

Dual branch mode sparing requires that all eight DIMM slots be populated and compliant with the

following population rules.

DIMM_A1 and DIMM_B1 must be identical in organization, size and speed.

DIMM_A2 and DIMM_B2 must be identical in organization, size and speed.

DIMM_C1 and DIMM_D1 must be identical in organization, size and speed.

DIMM_C2 and DIMM_D2 must be identical in organization, size and speed.

DIMM_A1 and DIMM_A2 should be identical in organization, size and speed. See note below.

DIMM_B1 and DIMM_B2 should be identical in organization, size and speed. See note below.

DIMM_C1 and DIMM_C2 should be identical in organization, size and speed. See note below.

DIMM_D1 and DIMM_D2 should be identical in organization, size and speed. See note below.

Sparing should be enabled in BIOS setup.

BIOS will configure Rank Sparing Mode.

The larger of the pairs {DIMM_A1, DIMM_B1} and {DIMM_A2, DIMM_B2} and {DIMM_C1,

DIMM_D1} and {DIMM_C2, DIMM_D2} will be selected as the spare pair units.

Revision 1.4

Intel order number: E15154-007

14

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

-

1

1

-

2

2

-

3

3

-

4

4

-

5

5

-

6

6

-

7

7

-

8

8

-

9

9

-

10

10

-

11

11

-

12

12

-

13

13

-

14

14

-

15

15

-

16

16

-

17

17

-

18

18

-

19

19

-

20

20

-

21

21

-

22

22

-

23

23

-

24

24

-

25

25

-

26

26

-

27

27

-

28

28

-

29

29

-

30

30

-

31

31

-

32

32

-

33

33

-

34

34

-

35

35

-

36

36

-

37

37

-

38

38

-

39

39

-

40

40

-

41

41

-

42

42

-

43

43

-

44

44

-

45

45

-

46

46

-

47

47

-

48

48

-

49

49

-

50

50

Intel MFS5000SIB Datasheet

- Category

- Server barebones

- Type

- Datasheet

- This manual is also suitable for

Ask a question and I''ll find the answer in the document

Finding information in a document is now easier with AI

Related papers

-

Intel SR1475NH1 - Server Platform - 0 MB RAM User manual

-

Intel MFSYS25V2 User manual

-

Intel MFS5000SI User manual

-

Intel MFS5000SI User manual

-

Intel DBS2600CW2 Datasheet

-

Intel MFS5520VI Datasheet

-

Fujitsu P4X-0373-2X2M-1066 Datasheet

-

Intel S3000PT User manual

-

Intel SR2520SAF Datasheet

-

Intel BB5000XVNSATAR Datasheet

Other documents

-

Gigabyte GS-R227E-RH Owner's manual

-

Hitachi CN7741-Y User manual

-

Smartech Products TECH-5000P User manual

Smartech Products TECH-5000P User manual

-

Dell PowerEdge 1900 User guide

-

Dell PowerEdge 1900 User guide

-

Dell PowerEdge 1900 User guide

-

Dell PowerEdge 1900 User guide

-

Dell PowerEdge 1900 User guide

-

Tyan S2696A2NRF Datasheet

-

Tyan S2692ANR Datasheet