A - 4 A - 4

* The manual number is given on the bottom left of the back cover.

Print Date * Manual Number Revision

Dec., 2008 SH (NA) 080041-K New models of the Universal model QCPU have been added.

Model addition

Q00UJCPU, Q00UCPU, Q01UCPU, Q10UDHCPU, Q10UDEHCPU,

Q20UDHCPU, Q20UDEHCPU

Partial correction

ABOUT MANUALS, GENERIC TERMS, Section 1.1, 1.2, Chapter 2,

Section 3.1.2, 4.3.1, 4.3.3, 5.2.2, Appendix 1, 2

Jul., 2009 SH (NA) 080041-L The serial number (first five digits) of the Universal model QCPU has

been upgraded to "11043".

Partial correction

Section 4.1, 4.7.1, 6.1.1

Jan., 2010 SH (NA) 080041-M Descriptions on MELSEC-L series modules have been added.

Partial correction

ABOUT MANUALS, GENERIC TERMS, Chapter 1, Section 1.2,

Chapter 2, Section 3.1.2, 3.1.3, 3.2.1, 3.2.2, 3.2.3, 3.2.5, 3.3.1, 4.2,

4.2.2, 4.2.7, 4.2.8, 4.2.9, 4.2.10, 4.2.11, 4.3.1, 4.3.3, 4.3.5, 4.4, 4.4.1,

4.4.2, 4.4.3, 4.4.4, 4.4.5, 4.4.6, 4.4.7, 4.4.8, 4.4.9, 4.4.10, 4.4.11, 4.5,

4.5.3, 4.6, 4.7, 4.7.1, 4.7.3, 4.7.4, 4.7.5, 4.7.6, 4.8.1, 4.8.2, 5.2, 5.2.1,

5.2.2, 5.2.3, 5.3.1, 6.1, 6.1.1, 6.3.1, 6.3.2, 6.4.3, 6.6, Appendix 1.1,

1.2, 3

Addition

CONDITIONS OF USE FOR THE PRODUCT, Section 3.2.4

Apr., 2010 SH (NA) 080041-N New models of the Universal model QCPU have been added.

Model addition

Q50UDEHCPU, Q100UDEHCPU

Partial correction

GENERIC TERMS, Chapter 2, Section 3.1.2, 3.3.1, 4.2, 4.2.8, 4.3.3,

5.2.2, Appendix 2

Aug., 2010 SH (NA) 080041-O The serial number (first five digits) of the Universal model QCPU has

been upgraded to "12052".

Partial correction

Section 3.1.2, 3.2.3, 3.3.2, 4.2, 4.2.8, 4.2.9, 4.4, 4.4.6, 4.4.8, 4.4.9,

4.5, 4.7, 4.7.5, 4.8, 4.8.1, 6.6, Appendix 1.1, 1.2

Addition

Section 6.6.1, 6.6.2, 6.6.3

Dec., 2010 SH (NA) 080041-P Partial correction

Section 4.3.4

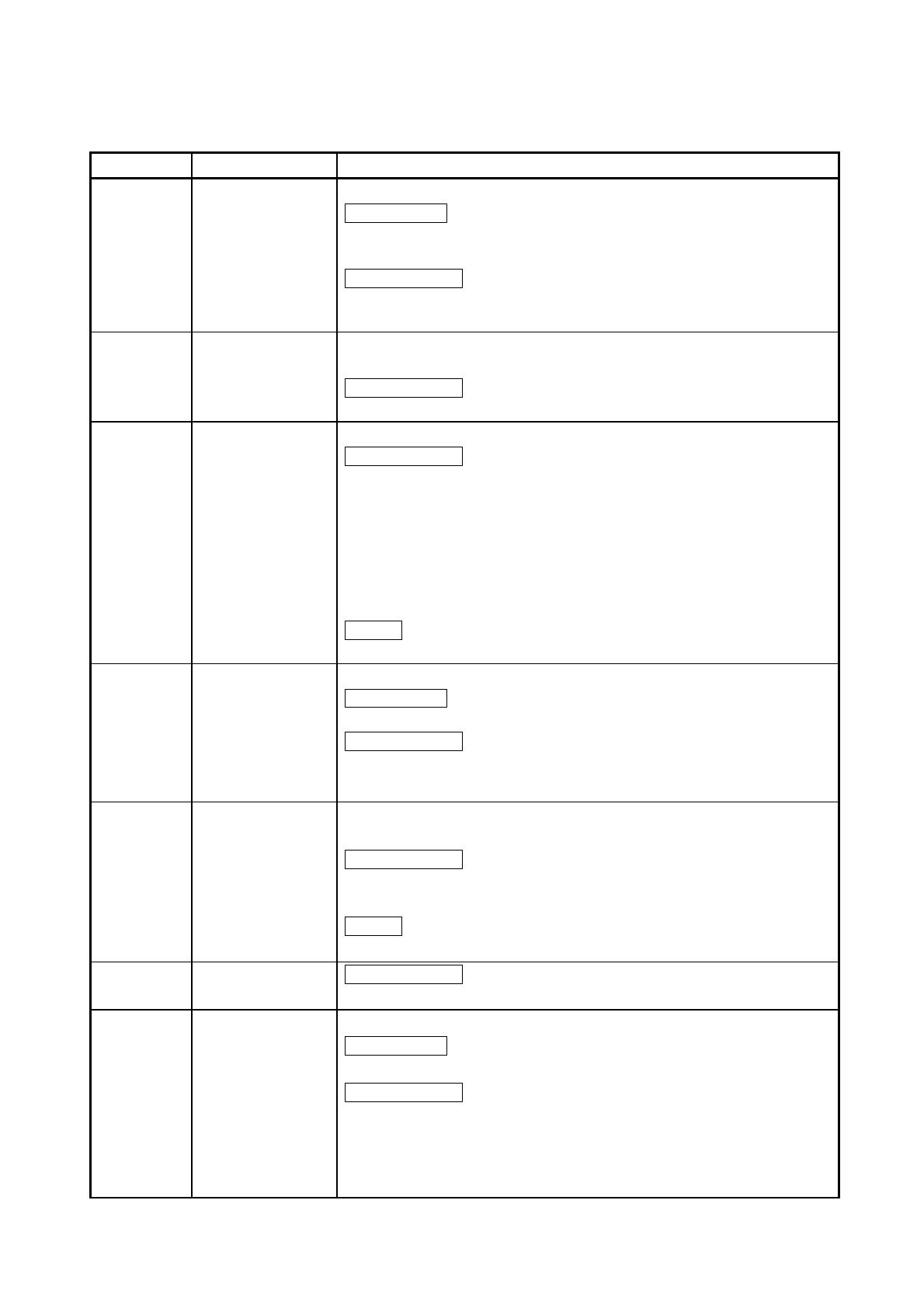

Jul., 2011 SH (NA) 080041-Q New models of the LCPU have been added.

Model addition

L02CPU-P, L26CPU-PBT

Partial correction

GENERIC TERMS, Section 1.2, Chapter 2, Section 3.1.2,

3.2.4, 3.3.1, 4.2, 4.2.8, 4.2.9, 4.3.1, 4.3.3, 5.2.2, Appendix 2