Altera Cyclone IV GX FPGA Reference guide

- Category

- Network switches

- Type

- Reference guide

This manual is also suitable for

© 2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

August 2015 Altera Corporation Cyclone IV GX FPGA Development Board

Reference Manual

ISO

9001:2008

Registered

August 2015 Altera Corporation Cyclone IV GX FPGA Development Board

Reference Manual

Contents

Chapter 1. Overview

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

Board Component Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

Development Board Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–3

Handling the Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–4

Chapter 2. Board Components

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

Board Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2

Featured Device: Cyclone IV GX Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–5

I/O Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–6

MAX II CPLD EPM2210 System Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–7

Configuration, Status, and Setup Elements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–12

Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–12

FPGA Configuration over Embedded USB-Blaster . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–12

FPGA Configuration from Flash Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–14

FPGA Configuration using External USB-Blaster . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–15

FPGA Configuration using EPCS Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–15

Status Elements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–16

Setup Elements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–17

Board Settings DIP Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–17

JTAG Chain Select DIP Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–18

PCIe Control DIP Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–19

Configuration Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–19

Configuration Push Buttons . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–20

Clock Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–20

General User Input/Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–21

User-Defined Push Buttons . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–21

User-Defined LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–22

General User-Defined LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–22

HSMC User-Defined LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–22

User-Defined DIP Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–23

LCD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–24

Components and Transceiver Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–26

PCIe . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–26

10/100/1000 Ethernet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–28

Transceiver Connector (Optional) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–29

High-Speed Mezzanine Cards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–30

Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–39

DDR2 SDRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–39

DDR2 SDRAM Top Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–40

DDR2 SDRAM Bottom Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–42

SSRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–44

Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–46

Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–47

Power Distribution System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–48

Power Measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–49

Statement of China-RoHS Compliance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–50

iv Contents

Cyclone IV GX FPGA Development Board August 2015 Altera Corporation

Reference Manual

Additional Information

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

How to Contact Altera . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

Typographic Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–2

August 2015 Altera Corporation Cyclone IV GX FPGA Development Board

Reference Manual

1. Overview

This document describes the hardware features of the Cyclone

®

IV GX FPGA

development board, including the detailed pin-out and component reference

information required to create custom FPGA designs that interface with all

components of the board.

General Description

The Cyclone IV GX FPGA development board provides a hardware platform for

developing and prototyping low-power, high-volume, feature-rich designs as well as

to demonstrate the Cyclone IV GX device's on-chip memory, embedded multipliers,

and the Nios

®

II embedded soft processor. The board provides peripherals and

memory interfaces to facilitate the development of the Cyclone IV GX FPGA designs.

f For more information on the Cyclone IV device family, refer to the Cyclone IV Device

Handbook.

Board Component Blocks

The board features the following major component blocks:

■ Cyclone IV GX EP4CGX150DF31 FPGA in the 896-pin FineLine BGA (FBGA)

package

■ 1.2-V core power

■ MAX

®

II EPM2210GF256 CPLD in the 256-pin FBGA package

■ 1.8-V core power

■ FPGA configuration circuitry

■ MAX

II CPLD EPM2210 System Controller and flash fast passive parallel (FPP)

configuration

■ Active serial configuration

■ On-board USB-Blaster

TM

for use with the Quartus

®

II Programmer

■ JTAG header for external USB-Blaster with the Quartus II Programmer

■ On-Board ports

■ Embedded USB-Blaster

■ One gigabit Ethernet port

■ Communication ports

■ PCI Express (PCIe) edge connector

■ 10/100/1000BASE-T Ethernet PHY with RJ-45 connector

■ Two High-Speed Mezzanine Card (HSMC) interfaces

1–2 Chapter 1: Overview

Board Component Blocks

Cyclone IV GX FPGA Development Board August 2015 Altera Corporation

Reference Manual

■ On-Board memory

■ 4-MB (x16) Synchronous Static Random Access Memory (SSRAM)

■ Two 32-MB (x32) DDR2 SDRAM

■ 64-MB flash

■ On-Board clocking circuitry

■ 50.000-MHz oscillator

■ 125.000-MHz oscillator

■ SMA clock input

■ SMA clock output

■ Programmable oscillator (default: 100.000-MHz)

■ General user I/O

■ LEDs and display

■ Eight FPGA user LEDs

■ One configuration done LED

■ One error LED

■ Five Ethernet status LEDs

■ One USB status LED

■ One power status LED

■ Five configuration LEDs

■ A two-line 16-character LCD display

■ Push buttons

■ One CPU reset push button

■ One MAX II configuration reset push button

■ One program-load push button—configure the FPGA from flash memory

■ One program-select push button—select image to load from flash memory

or serial configuration (EPCS) device

■ Four general user push buttons

■ DIP switches

■ Board settings DIP switch

■ JTAG chain select DIP switch

■ PCIe control DIP switch

■ Configuration settings DIP switch

■ User DIP switch

Chapter 1: Overview 1–3

Development Board Block Diagram

August 2015 Altera Corporation Cyclone IV GX FPGA Development Board

Reference Manual

■ Power supply

■ 16-V DC input

■ 2.5-mm barrel jack for DC power input

■ On/Off slide power switch

■ On-Board power measurement circuitry

■ 20-W per HSMC interface

■ Mechanical

■ PCIe small form factor board

■ Bench-top operation

Development Board Block Diagram

Figure 1–1 shows the block diagram of the Cyclone IV GX FPGA development board.

Figure 1–1. Cyclone IV GX FPGA Development Board Block Diagram

EP4CGX150DF31

XCVR x4

10/100/1000

Ethernet RGMII

Translator

User LEDs

Push-Button,

Switches

14-pin LCD

Header

CPLD

(x18)

64 MB Flash

(x16)

4 MB SSRAM

(x18)

RJ45

Jack

Power

Measure

1.8 V

CMOS

1.8 V

CMOS

LVDS

1.8 V

2.5 V

Port B

USB

Blaster

100 MHz XTAL

SMA Input

125 MHz XTAL

32 MB DDR2

(x32)

SMA Output

1.8 V

HSTL

32 MB DDR2

(x32)

Translator

Port A

Translator

For TX/RX

[8:16]

1.8 V

XCVR x4

2.5 V

1.8 V

2.5 V

1.8 V

x4 Edge

XCVR x4

2.5 V (For TX/RX [0:7])

1–4 Chapter 1: Overview

Handling the Board

Cyclone IV GX FPGA Development Board August 2015 Altera Corporation

Reference Manual

Handling the Board

When handling the board, it is important to observe the following static discharge

precaution:

c Without proper anti-static handling, the board can be damaged. Therefore, use

anti-static handling precautions when touching the board.

August 2015 Altera Corporation Cyclone IV GX FPGA Development Board

Reference Manual

2. Board Components

Introduction

This chapter introduces the major components on the Cyclone IV GX FPGA

development board. Figure 2–1 illustrates major component locations and Table 2–1

provides a brief description of all component features of the board.

1 A complete set of schematics, a physical layout database, and GERBER files for the

development board reside in the Cyclone IV GX FPGA development kit documents

directory.

f For information about powering up the board and installing the demonstration

software, refer to the Cyclone IV GX FPGA Development Kit User Guide.

This chapter consists of the following sections:

■ “Board Overview”

■ “Featured Device: Cyclone IV GX Device” on page 2–5

■ “MAX II CPLD EPM2210 System Controller” on page 2–7

■ “Configuration, Status, and Setup Elements” on page 2–12

■ “Clock Circuitry” on page 2–20

■ “General User Input/Output” on page 2–21

■ “Components and Transceiver Interfaces” on page 2–26

■ “Memory” on page 2–39

■ “Power Supply” on page 2–47

■ “Statement of China-RoHS Compliance” on page 2–50

2–2 Chapter 2: Board Components

Board Overview

Cyclone IV GX FPGA Development Board August 2015 Altera Corporation

Reference Manual

Board Overview

This section provides an overview of the Cyclone IV GX FPGA development board,

including an annotated board image and component descriptions. Figure 2–1

provides an overview of the development board features.

Table 2–1 describes the components and lists their corresponding board references.

Figure 2–1. Overview of the Cyclone IV GX FPGA Development Board Features

Clock Input

Differential

SMAs

Connectors

(J11, J12)

System Reset

Push-Button

Switch (S5)

Select

Push-Button

Switch (S7)

DC Input

Jack (J5)

Cyclone

IV GX

FPGA

(U10)

Character

LCD

(J13)

CPU Reset

Push-Button

Switch (S6)

Power

Switch

(SW3)

Clock Input

SMA

Connector

(J10)

Ethernet LEDs

(D24-D27)

MAX II CPLD

EPM2210

System Controller

(U7)

User LEDs

(D7-D10,

D12-D15)

Flash x16

Memory (U6)

PCI Express

Edge Connector

(J14)

USB Type-B

Connector (J4)

RJ-45 Connector

(J7)

JTAG

Connector

(J6)

Configuration Done, Load,

Error, EPCS, User,

and Factory LEDs (D16-D21)

Load

Push-Button

Switch (S8)

Power LED

(D11)

HSMC Port A

(J1)

User Push-Button

Switches (S1-S4)

User DIP

Switch

(SW2)

Clock output

SMA

Connector

(J9)

HSMC Port B

(J2)

Gigabit Ethernet

(U21)

HSMC Bank Selection

Jumper (J3)

Board Settings

DIP Switch

(SW1)

DDR2A x32

(U8, U15)

EPCS

Device

(U18)

PCI Express

Control

DIP Switch

(SW4)

DDR2B x32

(U17, U19)

JTAG Chain

Select DIP

Switch (SW5)

Table 2–1. Cyclone IV GX FPGA Development Board Components (Part 1 of 3)

Board Reference Type Description

Featured Devices

U10 FPGA EP4CGX150DF31, 896-pin FBGA.

U7 CPLD EPM2210GF256, 256-pin FBGA.

Configuration, Status, and Setup Elements

J4 USB Type-B connector Connects to the computer to enable embedded USB-Blaster JTAG.

J6 JTAG connector Disables embedded blaster (for use with external USB-Blasters).

U18

EPCS128 serial configuration

device

Flash memory device with a serial interface which stores

configuration data for FPGA device that supports active serial

configuration and reloads the data to the FPGA upon power-up or

reconfiguration.

Chapter 2: Board Components 2–3

Board Overview

August 2015 Altera Corporation Cyclone IV GX FPGA Development Board

Reference Manual

D17 Load LED

Illuminates when the MAX II CPLD EPM2210 System Controller is

actively configuring the FPGA.

D18 Error LED Illuminates when the FPGA configuration from flash memory fails.

D24–D27, D30,

D31

Ethernet LEDs Shows the connection speed as well as transmit or receive activity.

D11 Power LED Illuminates when 14-V – 20-V DC power is present.

D28 PCIe x4 LED You can configure this LED to illuminate when PCIe is in x4 mode.

D29 PCIe x1 LED You can configure these LEDs to illuminate when PCIe is in x1 mode.

SW4 PCIe DIP switch

Controls the PCIe lane width (connecting

prsnt

pins together on the

PCIe edge connector) or disables the embedded USB-Blaster.

SW5 JTAG chain select DIP switch

Enables and disables devices in the JTAG chain. The switch is located

under the character LCD.

SW1 Board settings DIP switch

Controls the Max II CPLD EPM2210 System Controller functions

such as enabling the 125-MHz clock or programmable clock, as well

as selection between the SMA clock input or the programmable clock

for buffer multiplexer.

S5 System reset push button Press to reset the MAX II CPLD EPM2210 System Controller.

S6 CPU reset push button Press to reset the FPGA logic.

S7 Program select push button

Toggles the LEDs which selects the program image that loads either

from the flash memory (FPP mode) or the EPCS device (active serial

mode) to the FPGA.

S8 Program load push button

Configure the FGPA from flash memory based on the program select

LEDs setting.

Clock Circuitry

X2 125-MHz oscillator 125-MHz crystal oscillator for general use such as memories.

X3 50-MHz oscillator

50-MHz crystal oscillator for configuration purpose. This oscillator is

located at the bottom of the board.

X5 25-MHz oscillator

25-MHz crystal oscillator for 10 Gigabit Ethernet. This oscillator is

located at the bottom of the board.

Y2 6-MHz oscillator

6-MHz crystal oscillator for USB PHY. This oscillator is located at the

bottom of the board.

X1 24-MHz oscillator

24-MHz crystal oscillator for USB PHY. This oscillator is located at

the bottom of the board.

X4 Programmable oscillator

Programmable oscillator for PCIe or general use such as memories.

Multiplexed with

CLKIN_SMA_P/N

signals based on

CLK_SEL

switch

value.

J11, J12 Clock input SMA

Drive LVPECL-compatible clock input into the clock multiplexer

buffer.

J10 Single-ended clock input 1.8-V single-ended clock input.

J9 Clock output SMA Drives out 2.5-V CMOS clock output from the FPGA.

Table 2–1. Cyclone IV GX FPGA Development Board Components (Part 2 of 3)

Board Reference Type Description

2–4 Chapter 2: Board Components

Board Overview

Cyclone IV GX FPGA Development Board August 2015 Altera Corporation

Reference Manual

General User Input/Output

D7–D10,

D12–D15

User LEDs Eight user LEDs. Illuminates when driven low.

S1–S4 User push buttons Four user push buttons. Driven low when pressed.

J13 Character LCD

Connector which interfaces to the provided 16 character × 2 line LCD

module.

Memory Devices

U44 SSRAM x18 memory

Standard synchronous RAM which provides a 72-Mbit (Mb) SSRAM

port. This SSRAM is located at the bottom of the board.

U6 Flash x64 memory

Synchronous burst mode flash device which provides a 256-Mb

non-volatile memory port.

U8, U15 DDR2 x32 SDRAM A Two 16-bit memory device.

U17, U19 DDR2 x32 SDRAM B Two 16-bit memory device.

Components Interfaces

J7 RJ-45 connector

Provides 10/100/1000 BASE-T Ethernet connection via a Marvell

88E1111 PHY and the FPGA-based Altera Triple Speed Ethernet

MegaCore function in RGMII mode.

U21 Gigabit Ethernet

A Marvell 88E1111 PHY device for 10/100/1000 BASE-T Ethernet

connection. The device is an auto-negotiating Ethernet PHY with an

RGMII interface to the FPGA.

J14 PCIe edge connector

Interfaces to a PCIe root port such as an appropriate PC

motherboard. Made of gold-plated edge fingers for up to ×4 signaling

in Gen1 mode.

J1 HSMC port A

Provides eight transceiver channels and 84 CMOS or 17 LVDS

channels per the HSMC specification.

J2 HSMC port B

Provides eight transceiver channels and 84 CMOS channels per the

HSMC specification.

Power Supply

J5 DC input jack

Accepts a 16-V DC power supply. Do not use this input jack while the

board is plugged into a PCIe slot.

SW3 Power switch

Switch to power on or off the board when power is supplied from the

DC input jack.

Table 2–1. Cyclone IV GX FPGA Development Board Components (Part 3 of 3)

Board Reference Type Description

Chapter 2: Board Components 2–5

Featured Device: Cyclone IV GX Device

August 2015 Altera Corporation Cyclone IV GX FPGA Development Board

Reference Manual

Featured Device: Cyclone IV GX Device

The Cyclone IV GX FPGA development board features the Cyclone IV GX

EP4CGX150DF31 device (U10) in a 896-pin FBGA package.

f For more information about Cyclone IV device family, refer to the Cyclone IV Device

Handbook.

Table 2–2 describes the features of the Cyclone IV GX EP4CGX150DF31 device.

Table 2–3 lists the Cyclone IV GX device component reference and manufacturing

information.

Table 2–2. Cyclone IV GX EP4CGX150DF31 Device Features

Equivalent LEs

Embedded

Memory (Kbits)

18-bit × 18-bit

Multipliers

Transceivers PLLs User I/O Package Type

149,760 6,480 360 8 8 475 896-pin FBGA

Table 2–3. Cyclone IV GX Device Component Reference and Manufacturing Information

Board Reference Description Manufacturer

Manufacturing

Part Number

Manufacturer

Website

U10

FPGA, Cyclone IV GX, 896-pin

FBGA package, lead-free.

Altera

Corporation EP4CGX150DF31 www.altera.com

2–6 Chapter 2: Board Components

Featured Device: Cyclone IV GX Device

Cyclone IV GX FPGA Development Board August 2015 Altera Corporation

Reference Manual

I/O Resources

Figure 2–2 illustrates the bank organization and I/O count for the EP4CGX150DF31

device in the 896-pin FBGA package.

Figure 2–2. EP4CGX150DF31 Device I/O Bank Diagram

(1)

Notes to Figure 2–2:

(1) This is a top view of the silicon die. For exact pin locations, refer to the pin list and the Quartus II software.

(2) True differential (PPDS, LVDS, mini-LVDS, and RSDS I/O standards) outputs are supported in row I/O banks 5 and 6 only. External resistors are

needed for the differential outputs in column I/O banks.

(3) The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

(4) The HSTL-12 Class II is supported in column I/O banks 4, 7, and 8.

(5) The differential SSTL-18 and SSTL-2, differential HSTL-18, and HSTL-15 I/O standards are supported only on clock input pins and phase-locked

loops (PLLs) output clock pins. PLL output clock pins do not support Class II interface type of differential SSTL-18, HSTL-18, HSTL-15, and

HSTL-12 I/O standards.

(6) The differential HSTL-12 I/O standard is only supported on clock input pins and PLL output clock pins. Differential HSTL-12 Class II is supported

only in column I/O banks 4, 7, and 8.

(7) BLVDS output uses two single-ended outputs with the second output programmed as inverted. BLVDS input uses the LVDS input buffer.

(8) The PCI-X I/O standard does not meet the IV curve requirement at the linear region.

(9) The OCT block is located in the shaded banks 4, 5, and 7.

(10) The dedicated clock input I/O banks 3A, 3B, 8A, and 8B can be used either for HSSI input reference clock pins or clock input pins.

(11) Single-ended clock input support is available for dedicated clock input I/O banks 3B and 8B.

Right, Top, and Bottom Banks Support:

3.3-V LVTTL/LVCMOS

3.0-V LVTTL/LVCMOS

2.5-V LVTTL/LVCMOS

1.8-V LVTTL/LVCMOS

1.5-V LVCMOS

1.2-V LVCMOS

PPDS

LVDS

RSDS

mini-LVDS

Bus LVDS (7)

LVPECL (3)

SSTL-2 class I and II

SSTL-18 CLass I and II

HSTL-18 Class I and II

HSTL-15 Class I and II

HSTL-12 Class I and II (4)

Differential SSTL-2 (5)

Differential SSTL-18 (5)

Differential HSTL-18 (5)

Differential HSTL-15 (5)

Differential HSTL-12 (6)

3.0-V PCI/PCI-X (8)

VCCIO9

Configuration

pins

Config

pins

VCCIO8 VCC_CLKIN8A

VCC_CLKIN3A

VCCIO7

VCCIO6

VCCIO5

VCCIO4VCCIO3

I/O Bank 9 I/O Bank 7

I/O Bank 4

I/O Bank 5

PCIe hard IP x1, x2, and x4

I/O Bank 6

VCC_CLKIN8B

VCCIO3 VCC_CLKIN3B

Ch0 Ch1 Ch2

GXBL0

Ch3 Ch0 Ch1 Ch2

GXBL1

Ch3

I/O bank with

calibration block

I/O bank without

calibration block

Calibration block

coverage

I/O Bank 8

I/O Bank

8A (10)

I/O Bank 8B

(10), (11)

I/O Bank 3

I/O Bank

3A (10)

I/O Bank 3B

(10), (11)

Chapter 2: Board Components 2–7

MAX II CPLD EPM2210 System Controller

August 2015 Altera Corporation Cyclone IV GX FPGA Development Board

Reference Manual

Table 2–4 lists the Cyclone IV GX device pin count and usage by function on the

development board.

MAX II CPLD EPM2210 System Controller

The board utilizes the EPM2210 System Controller, an Altera MAX

II CPLD, for the

following purposes:

■ FPGA configuration from flash memory

■ Power consumption monitoring

■ Virtual JTAG interface for PC-based GUI

■ Control registers for clocks

■ Control registers for remote system update

Table 2–4. Cyclone IV GX Device I/O Pin Count and Usage

Function I/O Standard I/O Count Special Pins

Clocks or Oscillators 1.8-V CMOS 9 3 clock inputs, 1 clock input

DDR2A x32 (Top) 1.8-V SSTL 63 —

DDR2B x32 (Bottom) 1.8-V SSTL 63 —

Flash, SSRAM, MAX 1.8-V CMOS 55 —

Gigabit Ethernet 2.5-V CMOS

(1)

16 —

User I/O (LEDs, Push buttons) 1.8-V 25 —

14-pin LCD 2.5-V CMOS

(1)

11 —

HSMC Port A 2.5-V/1.8-V CMOS 103 —

HSMC Port B 2.5-V CMOS

(1)

87 —

PCIe x4 2.5-V CMOS 7 —

PCIe (for HSMC port B transceiver multiplexer) XCVR 16 —

Passive serial and active serial configuration 2.5-V CMOS 21 —

Device I/O Total:

476

Note to Table 2–4:

(1) Translated from 1.8-V to 2.5-V using a bidirectional voltage translator.

2–8 Chapter 2: Board Components

MAX II CPLD EPM2210 System Controller

Cyclone IV GX FPGA Development Board August 2015 Altera Corporation

Reference Manual

Figure 2–3 illustrates the MAX II CPLD EPM2210 System Controller's functionality

and external circuit connections as a block diagram.

Table 2–5 lists the I/O signals present on the MAX

II CPLD EPM2210 System

Controller. The signal names and functions are relative to the MAX

II device (U7).

Figure 2–3. MAX II CPLD EPM2210 System Controller Block Diagram

Information

Register

MAX II

Embedded

USB-Blaster

MAX II CPLD EPM2210 System Controller

Power

Calculations

SLD-HUB

PFL

Power

Measurement

Results

Virtual-JTAG

PC

EP4CGX150

EPCS

LTC2418

Controller

FLASH

Decoder

Encoder

JTAG Control

Control

Register

Clock

Controller

Programmable

Clock

Configuration State

Machine

User/Factory

DIP Switch

Configuration

Push Buttons

Configuration

Signals (GPIO on

MAX Device)

Configuration

Status LEDs

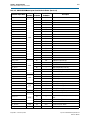

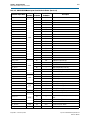

Table 2–5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 1 of 4)

Schematic Signal Name

I/O

Standard

EPM2210

Pin Number

EP4CGX15BF14

Pin Number

Description

CLKA_EN

2.5-V

H3 — 125-MHz oscillator enable

CLKA_SDA

J1 — 125-MHz programming data

CLKA_SCL

H4 — 125-MHz programming clock

CLK125_EN

J2 — 125-MHz oscillator enable

CLKIN_50

H5 — 50-MHz oscillator

CLKIN_MAX_100

J5 — MAX II clock input

FAN_CNTL

P2 — Fan control

Chapter 2: Board Components 2–9

MAX II CPLD EPM2210 System Controller

August 2015 Altera Corporation Cyclone IV GX FPGA Development Board

Reference Manual

FACTORY_CONFIGn

1.8-V

G12 — Factory configuration enable

FLASH_ADVn

L13 F24 FSM bus flash memory address valid

FLASH_RESETn

M15 A28 FSM bus flash memory reset

FLASH_WEn

L12 C13 FSM bus flash memory write enable

FLASH_OEn

M16 F7 FSM bus flash memory output enable

FLASH_RDYBSYn

L11 B7 FSM bus flash memory ready

FLASH_CLK

L15 Y21 FSM bus flash memory clock

FLASH_CEn

K14 E25 FSM bus flash memory chip enable

FPGA_DATA0

2.5-V

D3 A3 FPGA data

FPGA_DATA1

L1 G9 FPGA data

FPGA_DATA2

J16 H9 FPGA data

FPGA_DATA3

J13 D1 FPGA data

FPGA_DATA4

H16 C2 FPGA data

FPGA_DATA5

H13 AE4 FPGA data

FPGA_DATA6

H15 AE5 FPGA data

FPGA_DATA7

H14 AE10 FPGA data

FPGA_DCLK

C2 B3 FPGA configuration clock

FPGA_CONF_DONE

E3 B1 FPGA configuration done

FPGA_STATUSn

C3 AJ1 FPGA configuration ready

FPGA_CONFIGn

E4 AB9 FPGA configuration active

JTAG_TCK

P3 F2 FPGA JTAG TCK

JTAG_TMS

N4 E1 FPGA JTAG TMS

JTAG_FPGA_TDO

L6 F1 FPGA JTAG TDO

JTAG_EPM2210_TDO

M5 E2 MAX II JTAG TDO

Table 2–5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 2 of 4)

Schematic Signal Name

I/O

Standard

EPM2210

Pin Number

EP4CGX15BF14

Pin Number

Description

2–10 Chapter 2: Board Components

MAX II CPLD EPM2210 System Controller

Cyclone IV GX FPGA Development Board August 2015 Altera Corporation

Reference Manual

FSM_A1

1.8-V

P7 AD6 FSM bus address

FSM_A2

R6 AK29 FSM bus address

FSM_A3

R5 AA21 FSM bus address

FSM_A4

R4 AG25 FSM bus address

FSM_A5

R3 AH5 FSM bus address

FSM_A6

M8 AH27 FSM bus address

FSM_A7

P6 AJ12 FSM bus address

FSM_A8

P8 AF16 FSM bus address

FSM_A9

R7 AH20 FSM bus address

FSM_A10

N6 AK23 FSM bus address

FSM_A11

P4 AH17 FSM bus address

FSM_A12

P5 AB21 FSM bus address

FSM_A13

N8 AF19 FSM bus address

FSM_A14

T6 AF12 FSM bus address

FSM_A15

N5 AG27 FSM bus address

FSM_A16

M6 AK26 FSM bus address

FSM_A17

N7 AH4 FSM bus address

FSM_A18

T5 AK3 FSM bus address

FSM_A19

R1 AH9 FSM bus address

FSM_A20

M7 AG6 FSM bus address

FSM_A21

T2 AK25 FSM bus address

FSM_A22

T7 AE21 FSM bus address

FSM_A23

T4 AA18 FSM bus address

Table 2–5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 3 of 4)

Schematic Signal Name

I/O

Standard

EPM2210

Pin Number

EP4CGX15BF14

Pin Number

Description

Chapter 2: Board Components 2–11

MAX II CPLD EPM2210 System Controller

August 2015 Altera Corporation Cyclone IV GX FPGA Development Board

Reference Manual

FSM_A24

1.8-V

R8 AK27 FSM bus address

FSM_A25

M9 AF21 FSM bus address

FSM_D0

E9 AK14 FSM bus data

FSM_D1

A9 AE6 FSM bus data

FSM_D2

E7 AG21 FSM bus data

FSM_D3

B7 AE9 FSM bus data

FSM_D4

A6 AK28 FSM bus data

FSM_D5

A8 AD23 FSM bus data

FSM_D6

C7 AG24 FSM bus data

FSM_D7

B6 AB22 FSM bus data

FSM_D8

E8 AE22 FSM bus data

FSM_D9

B8 AJ24 FSM bus data

FSM_D10

D8 Y19 FSM bus data

FSM_D11

D7 AH23 FSM bus data

FSM_D12

A7 AK22 FSM bus data

FSM_D13

C8 AH24 FSM bus data

FSM_D14

B5 Y18 FSM bus data

FSM_D15

A5 AJ13 FSM bus data

HSMA_PSNTn

2.5-V

G5 A25 HSMC port A present LED

HSMB_PSNTn

H2 C26 HSMC port B present LED

MAX_EPCS

G3 — MAX II EPCS memory chip enable

MAX_ERROR

G2 — FPGA configuration error LED

MAX_FACTORY

G4 — FPGA factory configuration LED

MAX_USER

G1 — FPGA user configuration LED

MAX_FAN

1.8-V

B1 — FPGA fan LED

MAX_CSn

L16 B12 MAX II chip select

MAX_OEn

K13 G8 MAX II output enable

MAX_WEn

K15 A9 MAX II write enable

MSEL0

2.5-V

L2 AD7 FPGA MSEL0 configuration mode select

MSEL2

M1 AC7 FPGA MSEL2 configuration mode select

MSEL3

M2 AC8 FPGA MSEL3 configuration mode select

RESET_CONFIGn

1.8-V G16 AF27 Force FPGA configuration push button

SENSE_CSn

2.5-V

F5 — Power monitor chip select

SENSE_SCK

E1 —

Power monitor serial peripheral interface (SPI)

clock

SENSE_SDI

F4 — Power monitor SPI data in

SENSE_SDO

E2 — Power monitor SPI data out

SYS_RESETn

1.8-V J15 AF27 System reset push button

USER_FACTORY

2.5-V N1 — User reset push button

Table 2–5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 4 of 4)

Schematic Signal Name

I/O

Standard

EPM2210

Pin Number

EP4CGX15BF14

Pin Number

Description

2–12 Chapter 2: Board Components

Configuration, Status, and Setup Elements

Cyclone IV GX FPGA Development Board August 2015 Altera Corporation

Reference Manual

Table 2–6 lists the MAX

II CPLD EPM2210 System Controller component reference

and manufacturing information.

Configuration, Status, and Setup Elements

This section describes the board's configuration, status, and setup elements.

Configuration

This section describes the FPGA, flash memory, and MAX

II CPLD EPM2210 System

Controller device configuration methods supported by the Cyclone IV GX FPGA

development board. The Cyclone IV GX FPGA development board supports the

following configuration methods:

■ Embedded USB-Blaster is the default method for configuring the FPGA at any

time using the Quartus II Programmer in JTAG mode with the supplied USB cable.

■ Flash memory download is used for storing FPGA images which the MAX

II

CPLD EPM2210 System Controller uses to configure the Cyclone IV GX device

either on board power-up or after the program load push-button switch (S8) is

pressed.

■ External USB-Blaster for configuring the FPGA using an external USB-Blaster.

■ Serial configuration (EPCS) device (U18) is used to store configuration data for

FPGA device that supports active serial (AS) configuration and reloads the data to

the FPGA upon reconfiguration. Use the program select push-button switch (S7) to

select the configuration files to be loaded from either page 0 (factory location),

page 1 (user location), or from the EPCS device.

FPGA Configuration over Embedded USB-Blaster

The USB-Blaster is implemented using a USB Type-B connector (J4), a FTDI USB 2.0

PHY device (U4), and an Altera MAX II CPLD (U7). This allows the configuration of

the FPGA using a USB cable directly connected between the USB port on the board

(J4) and a USB port of a PC running the Quartus II software. The JTAG chain is

normally mastered by the embedded USB-Blaster found in the MAX

II CPLD

EPM2210 System Controller.

Table 2–6. MAX II CPLD EPM2210 System Controller Component Reference and Manufacturing Information

Board Reference Description Manufacturer

Manufacturing

Part Number

Manufacturer

Website

U7

IC - MAX II CPLD EPM2210G

256FBGA -3 LF 1.8V VCCINT

Altera

Corporation EPM2210GF256C3N www.altera.com

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

Page is loading ...

-

1

1

-

2

2

-

3

3

-

4

4

-

5

5

-

6

6

-

7

7

-

8

8

-

9

9

-

10

10

-

11

11

-

12

12

-

13

13

-

14

14

-

15

15

-

16

16

-

17

17

-

18

18

-

19

19

-

20

20

-

21

21

-

22

22

-

23

23

-

24

24

-

25

25

-

26

26

-

27

27

-

28

28

-

29

29

-

30

30

-

31

31

-

32

32

-

33

33

-

34

34

-

35

35

-

36

36

-

37

37

-

38

38

-

39

39

-

40

40

-

41

41

-

42

42

-

43

43

-

44

44

-

45

45

-

46

46

-

47

47

-

48

48

-

49

49

-

50

50

-

51

51

-

52

52

-

53

53

-

54

54

-

55

55

-

56

56

-

57

57

-

58

58

-

59

59

-

60

60

Altera Cyclone IV GX FPGA Reference guide

- Category

- Network switches

- Type

- Reference guide

- This manual is also suitable for

Ask a question and I''ll find the answer in the document

Finding information in a document is now easier with AI

Related papers

-

Terasic Cyclone IV GX Reference guide

Terasic Cyclone IV GX Reference guide

-

Altera Cyclone III LS Reference guide

-

Altera MAX V CPLD Reference guide

-

Altera Arria II GX Reference guide

-

Altera Arria V GX Reference guide

-

Altera Arria II GX Reference guide

-

Altera Cyclone III Reference guide

-

Altera Cyclone V E FPGA Reference guide

-

Terasic Stratix IV GX User guide

Terasic Stratix IV GX User guide

-

Altera Cyclone III Reference guide